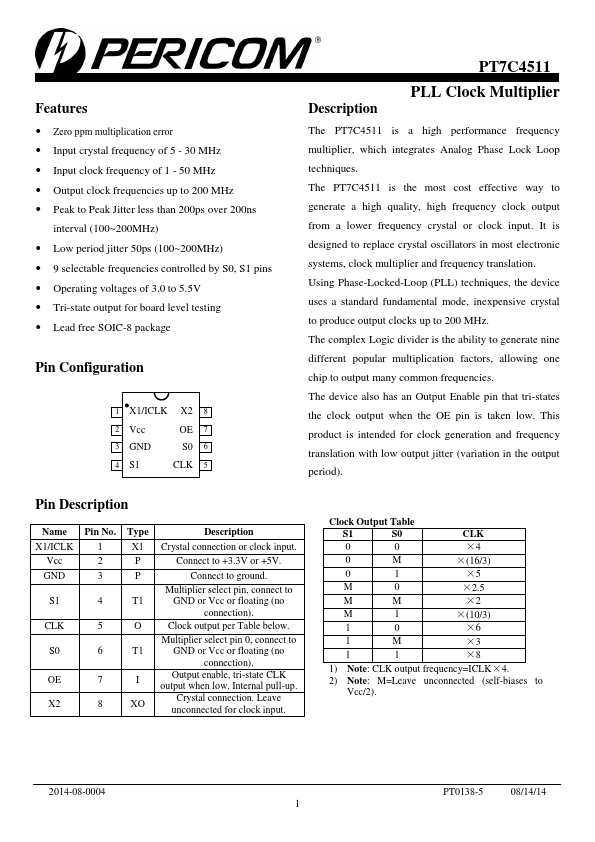

PT7C4511 Overview

Key Specifications

Package: SOP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Description

Zero ppm multiplication error The PT7C4511 is a high performance frequency - Input crystal frequency of 5 - 30 MHz multiplier, which integrates Analog Phase Lock Loop - Input clock frequency of 1 - 50 MHz techniques. Output clock frequencies up to 200 MHz - Peak to Peak Jitter less than 200ps over 200ns interval (100~200MHz) - Low period jitter 50ps (100~200MHz) - 9 selectable frequencies controlled by S0, S1 pins - Operating voltages of 3.0 to 5.5V - Tri-state output for board level testing - Lead free SOIC-8 package The PT7C4511 is the most cost effective way to generate a high quality, high frequency clock output from a lower frequency crystal or clock input.