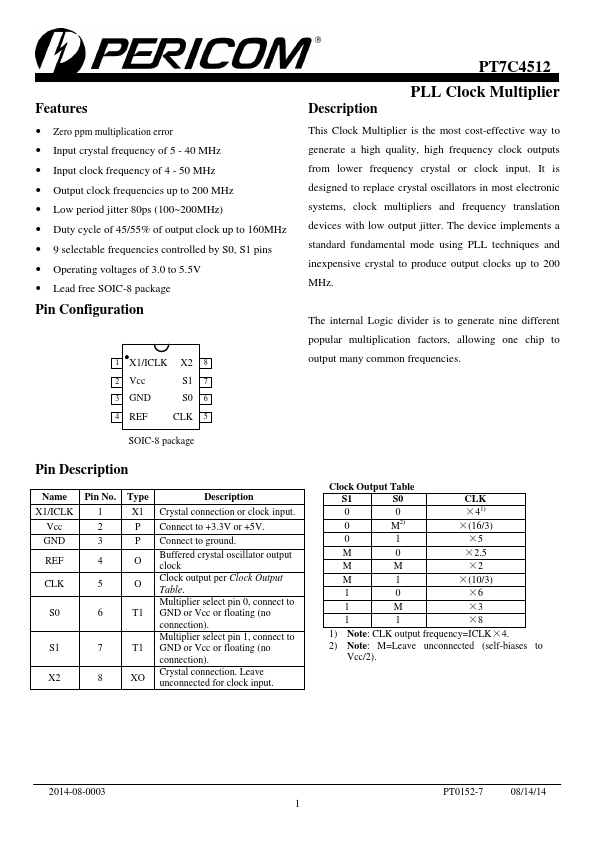

| Part | PT7C4512 |

|---|---|

| Description | PLL Clock Multiplier |

| Manufacturer | Pericom Semiconductor |

| Size | 221.72 KB |

Pricing from 0.28 USD, available from Component Stockers USA and Win Source.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Component Stockers USA | 13627 | 1+ : 0.28 USD 10+ : 0.28 USD 100+ : 0.27 USD 1000+ : 0.26 USD |

View Offer |

| Win Source | 78000 | 150+ : 0.386 USD 365+ : 0.3169 USD 565+ : 0.3069 USD 780+ : 0.297 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AD835 | Analog Devices | 4-Quadrant Multiplier |

| AD734 | Analog Devices | 10 MHz/ 4-Quadrant Multiplier/Divider |

| HA1-2556883 | Intersil | Wideband Four Quadrant Analog Multiplier (Voltage Output) |