PL613-21 Overview

Description

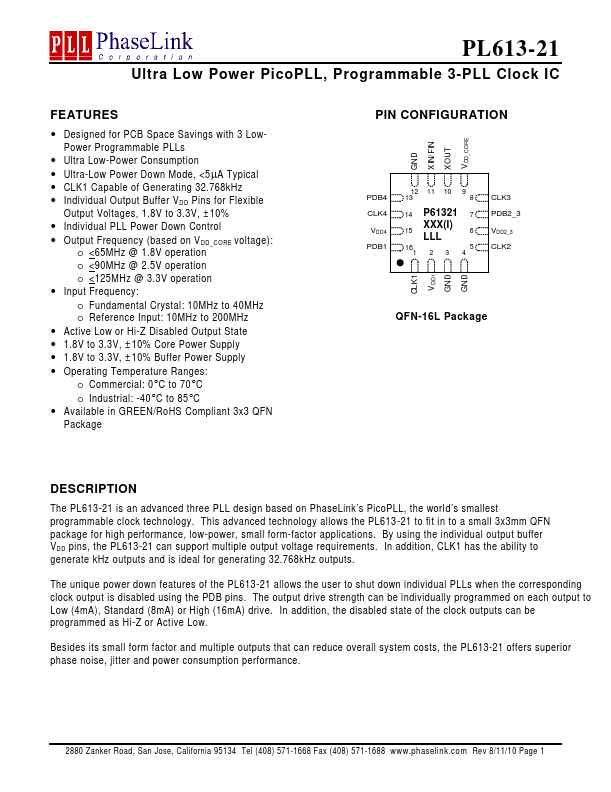

The PL613-21 is an advanced three PLL design based on PhaseLink’s PicoPLL, the world’s smallest programmable clock technology. This advanced technology allows the PL613-21 to fit in to a small 3x3mm QFN package for high performance, low-power, small form-factor applications.

Key Features

- Designed for PCB Space Savings with 3 LowPower Programmable PLLs

- Ultra Low-Power Consumption

- Ultra-Low Power Down Mode, <5A Typical

- CLK1 Capable of Generating 32.768kHz

- Individual Output Buffer VDD Pins for Flexible Output Voltages, 1.8V to 3.3V, ±10%

- Individual PLL Power Down Control

- Output Frequency (based on VDD_CORE voltage): o <65MHz @ 1.8V operation o <90MHz @ 2.5V operation o <125MHz @ 3.3V operation

- Input Frequency: o Fundamental Crystal: 10MHz to 40MHz o Reference Input: 10MHz to 200MHz

- Active Low or Hi-Z Disabled Output State

- 1.8V to 3.3V, ±10% Core Power Supply