PLL520-30

PLL520-30 is PECL and LVDS Low Phase Noise VCXO manufactured by PhaseLink Corporation.

FEATURES

- -

- -

- -

- -

- 65MHz to 130MHz Fundamental Mode Crystal. Output range: 65MHz

- 130MHz (no PLL). Low Injection Power for crystal 50u W. plementary outputs: PECL or LVDS. Selectable OE Logic Integrated variable capacitors. Supports 2.5V or 3.3V-Power Supply. Available in die form. Thickness 10 mil.

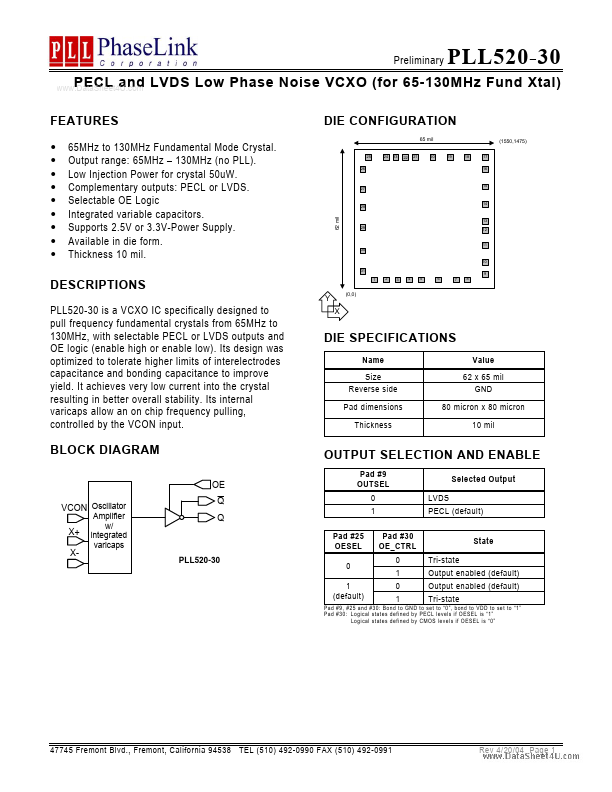

(1550,1475)

62 mil

13 29 12

11 30 10 31 9 1 2 3 4 5 6 7 8

DESCRIPTIONS

(0,0)

PLL520-30 is a VCXO IC specifically designed to pull frequency fundamental crystals from 65MHz to 130MHz, with selectable PECL or LVDS outputs and OE logic (enable high or enable low). Its design was optimized to tolerate higher limits of interelectrodes capacitance and bonding capacitance to improve yield. It achieves very low current into the crystal resulting in better overall stability. Its internal varicaps allow an on chip frequency pulling, controlled by the VCON input.

DIE SPECIFICATIONS

Name Size Reverse side Pad dimensions Thickness Value 62 x 65 mil GND 80 micron x 80 micron 10 mil

BLOCK DIAGRAM

OE VCON Oscillator X+ XQ Q

Amplifier w/ integrated varicaps

OUTPUT SELECTION AND ENABLE

Pad #9 OUTSEL 0 1 Pad #25 OESEL

Selected Output LVDS PECL (default)

Pad #30 OE_CTRL 0 1 0 1

State Tri-state Output enabled (default) Output enabled (default) Tri-state

0 1 (default)

Pad #9, #25 and #30: Bond to GND to set to “0”, bond to VDD to set to “1” Pad #30: Logical states defined by PECL levels if OESEL is “1” Logical states defined by CMOS levels if OESEL is “0”

47745 Fremont Blvd., Fremont, California 94538 TEL (510) 492-0990 FAX (510) 492-0991

Rev 4/20/04 Page 1

Preliminary

..

PECL and LVDS Low Phase Noise VCXO (for 65-130MHz Fund Xtal)

ELECTRICAL SPECIFICATIONS

1. Absolute Maximum Ratings PARAMETERS

Supply Voltage Input Voltage, dc Output Voltage, dc Storage Temperature Ambient Operating Temperature- Junction Temperature Lead Temperature (soldering, 10s) Input Static Discharge Voltage...