PLL601-12 Overview

Description

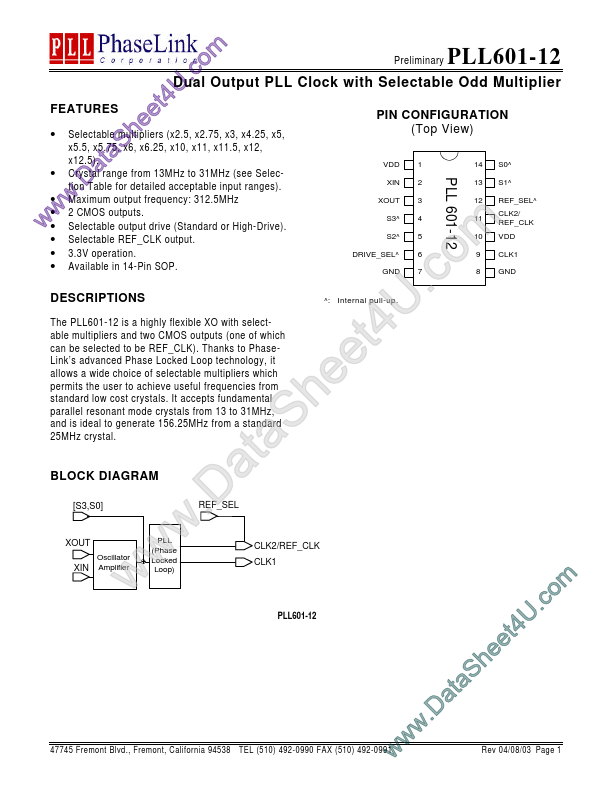

The PLL601-12 is a highly flexible XO with selectable multipliers and two CMOS outputs (one of which can be selected to be REF_CLK). Thanks to PhaseLink’s advanced Phase Locked Loop technology, it allows a wide choice of selectable multipliers which permits the user to achieve useful frequencies from standard low cost crystals.

Key Features

- Crystala range from 13MHz to 31MHz (see SelecD tion Table for detailed acceptable input ranges)

- w Maximum output frequency: 312.5MHz

- w 2 CMOS outputs. w