74F395

Overview

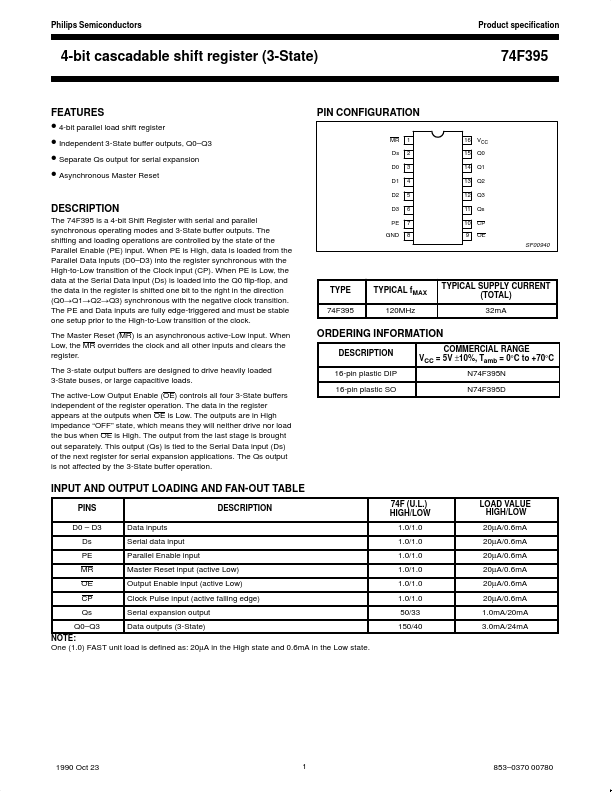

The 74F395 is a 4-bit Shift Register with serial and parallel synchronous operating modes and 3-State buffer outputs. The shifting and loading operations are controlled by the state of the Parallel Enable (PE) input.

- 4-bit parallel load shift register

- Independent 3-State buffer outputs, Q0-Q3

- Separate Qs output for serial expansion

- Asynchronous Master Reset