ISP1040C

ISP1040C is Intelligent SCSI Processor manufactured by QLogic Corporation.

QLogic Corporation

ISP1040C Intelligent SCSI Processor

Data Sheet

Features s s s s s s s s s s s s s

PCI Local Bus Specification revision 2.1 pliant pliance with ANSI SCSI standard X3.131-1994 pliance with ANSI X3T10/855D SCSI-3 parallel interface (SPI) standard pliance with ANSI X3T10/1071D Fast-20 standard pliance with PCI Bus Power Management Interface Specification Revision 1.0 (PC97) Onboard RISC processor to execute operations at the I/O control block level from the host memory Supports fast, wide, and Ultra (Fast-20) SCSI data transfer rates SCSI initiator and target modes of operation 32-bit, intelligent bus master, DMA PCI bus interface

Supports PCI dual-address cycle (64-bit addressing) SCSI operations executed from start to finish without host intervention Simultaneous, multiple logical threads JTAG boundary scan support

Product Description

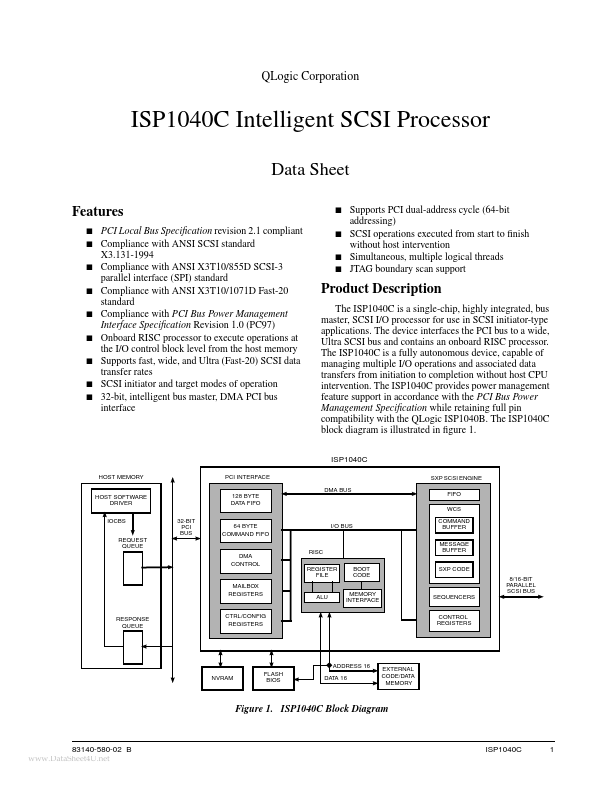

The ISP1040C is a single-chip, highly integrated, bus master, SCSI I/O processor for use in SCSI initiator-type applications. The device interfaces the PCI bus to a wide, Ultra SCSI bus and contains an onboard RISC processor. The ISP1040C is a fully autonomous device, capable of managing multiple I/O operations and associated data transfers from initiation to pletion without host CPU intervention. The ISP1040C provides power management feature support in accordance with the PCI Bus Power Management Specification while retaining full pin patibility with the QLogic ISP1040B. The ISP1040C block diagram is illustrated in figure 1.

HOST MEMORY HOST SOFTWARE DRIVER IOCBS REQUEST QUEUE 32-BIT PCI BUS

PCI INTERFACE DMA BUS 128 BYTE DATA FIFO

SXP SCSI ENGINE FIFO WCS

64 BYTE MAND FIFO RISC

I/O BUS

MAND BUFFER MESSAGE BUFFER BOOT CODE SXP CODE 8/16-BIT PARALLEL SCSI BUS SEQUENCERS CONTROL REGISTERS

DMA CONTROL

REGISTER FILE

MAILBOX REGISTERS

MEMORY INTERFACE

RESPONSE QUEUE

CTRL/CONFIG REGISTERS

ADDRESS 16 NVRAM FLASH BIOS DATA 16

EXTERNAL CODE/DATA MEMORY

Figure 1....