- Part: HYB18T1G160BC

- Description: 1-Gbit Double-Data-Rate-Two SDRAM

- Manufacturer: Qimonda

- Size: 3.86 MB

Page 2

Page 2

Page 3

Page 3

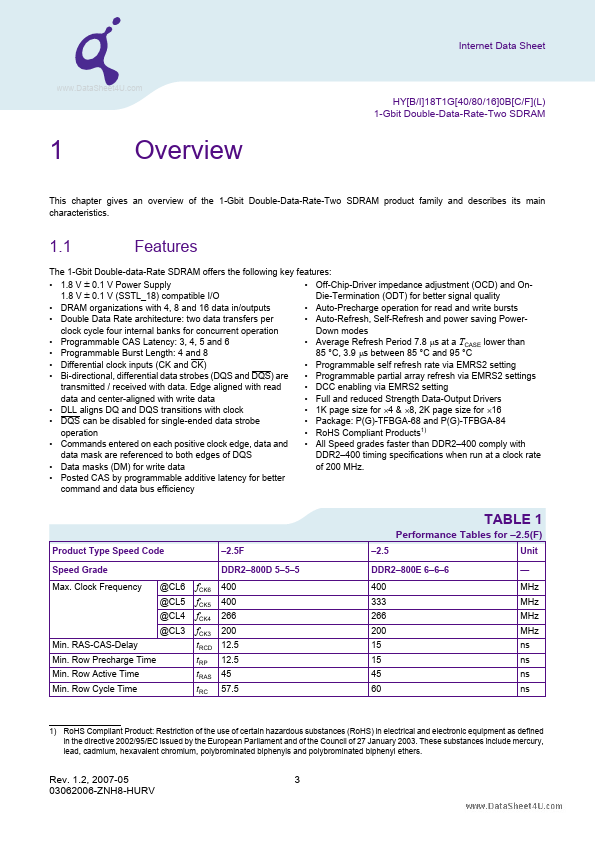

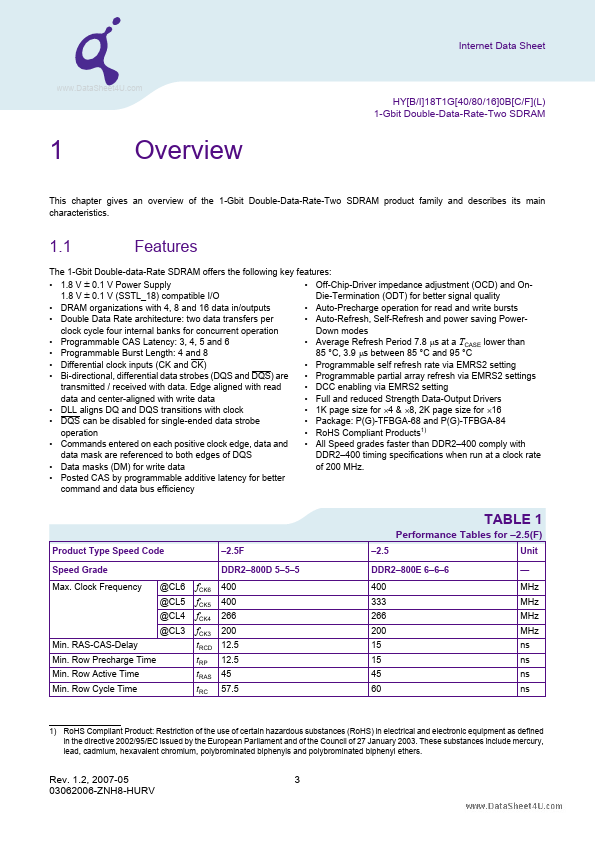

HYB18T1G160BC Key Features

- Off-Chip-Driver impedance adjustment (OCD) and On- 1.8 V ± 0.1 V Power Supply 1.8 V ± 0.1 V (SSTL_18) patible I/O Die-Te

- DRAM organizations with 4, 8 and 16 data in/outputs

- Auto-Precharge operation for read and write bursts

- Auto-Refresh, Self-Refresh and power saving Powerclock cycle four internal banks for concurrent operation Down modes

- Programmable CAS Latency: 3, 4, 5 and 6

- Average Refresh Period 7.8 µs at a TCASE lower than

- Programmable Burst Length: 4 and 8 85 °C, 3.9 µs between 85 °C and 95 °C

- Differential clock inputs (CK and CK)

- Programmable self refresh rate via EMRS2 setting

- Programmable partial array refresh via EMRS2 settings

Other HYB18T1G160BC Datasheets

| Manufacturer |

Part Number |

Description |

Infineon

Infineon |

HYB18T1G160AF

|

1 Gbit DDR2 SDRAM |