R8A66174SP

R8A66174SP is PARALLEL-IN SERIAL-OUT DATA BUFFER manufactured by Renesas.

DESCRIPTION

The R8A66174 is a CMOS LSI with 63-byte FIFO (First-In First-Out Memory). The mands or up to 63bytes data can be stored from 8-bit data bus. The data stored in FIFO can be outputted as serial data by executing mand, and when the stored data is outputted all, R8A66174 will output an interrupt request signal. R8A66174 has 2-bit output pins (/OE, LATCH) which can set/reset outside devices by the mand, R8A66174 can be connected to peripheral circuits that have a serial latch structure. R8A66174 is the succession product of M66300.

FEATURES

- General-purpose .. 8-bit CPU bus patible

- Built-in 63-byte FIFO

- High-speed output (10Mbps)

- It’s able to connect to LED array driver such as R8A66160 or R8A66161 directly

- Low-noise, high-output circuit IOL=16m A, IOH=-16m A (IOL=4m A, IOH=-4m A for /INT)

- Schmitt input (/RESET)

- Wide operating supply voltage range (Vcc=3.0~3.6V or Vcc=4.5~5.5V) o

- Wide operating temperature range (Ta=-40~85 C)

APPLICATION

General digital equipment for industrial and home use, panel display controllers, and eraser unit controller for copying machine.

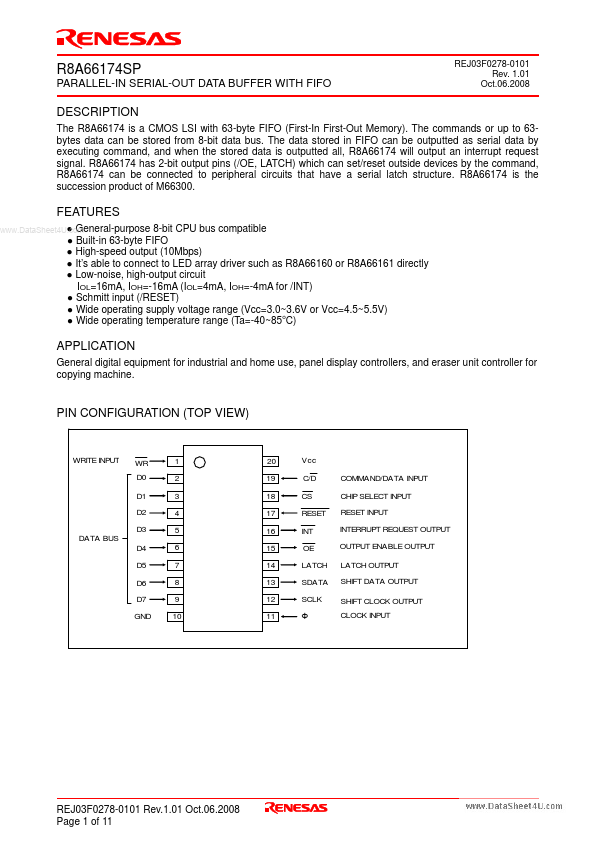

PIN CONFIGURATION (TOP VIEW)

WRITE INPUT

WR D0 D1 D2 D3

1 2 3 4 5 6 7 8 9 10

20 19 18 17 16 15 14 13 12 11

Vcc C/D CS RESET INT OE LATCH SDATA SCLK Φ MAND/DATA INPUT CHIP SELECT INPUT RESET INPUT INTERRUPT REQUEST OUTPUT OUTPUT ENABLE OUTPUT LATCH OUTPUT SHIFT DATA OUTPUT SHIFT CLOCK OUTPUT CLOCK INPUT

DATA BUS D4 D5 D6 D7 GND

REJ03F0278-0101 Rev.1.01 Oct.06.2008 Page 1 of 11

R8A66174SP BLOCK DIAGRAM

D0 D1 D2 D3 D4 D5 D6 D7

2 3 4 5 6 7 8 9 WR CK 8 SELECTOR 13

SDATA

DATA BUS

63 X 8-BIT SRAM

SHIFT DATA OUTPUT

LOAD

8-BIT SHIFT REGISTER

DECODER

SELECTOR

MAND/ DATA INPUT CHIP SELECT INPUT WRITE INPUT

C/D 19 CS 18 WR 1

INPUT CONTROL CIRCUIT

MATCHING DETECTION CIRCUIT WRITE COUNTER READ COUNTER

RD RD...

Representative R8A66174SP image (package may vary by manufacturer)