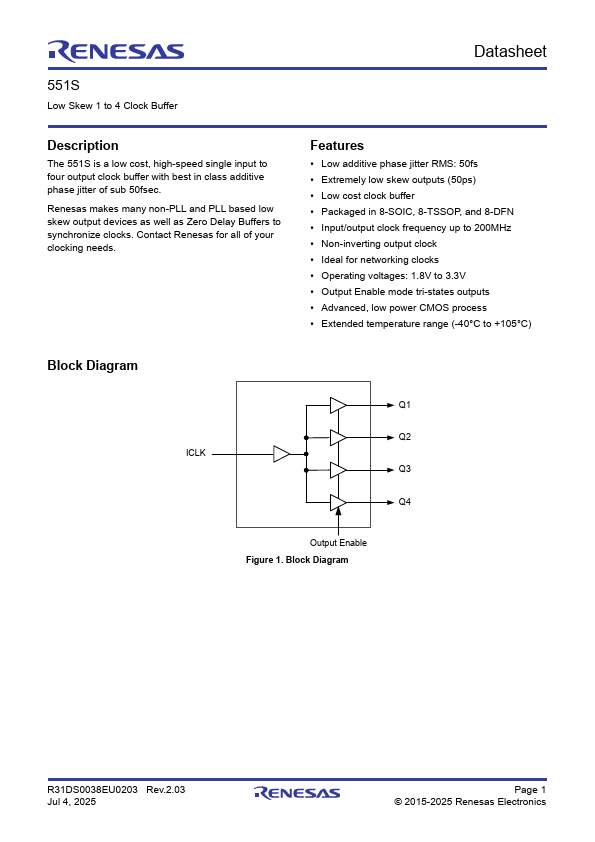

- Part: 551S

- Description: Low Skew 1 to 4 Clock Buffer

- Manufacturer: Renesas

- Size: 1.11 MB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| KR42JM4-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KR42HM4-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT86LM1-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT56QM1-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT50LM1-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT42HM4-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT42EM4-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT42HM1-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT42KM06-551 | Servo | 3-Phase Hybrid Stepping Motor |

| KT42EM1-551 | Servo | 3-Phase Hybrid Stepping Motor |