5P49V60B

Description

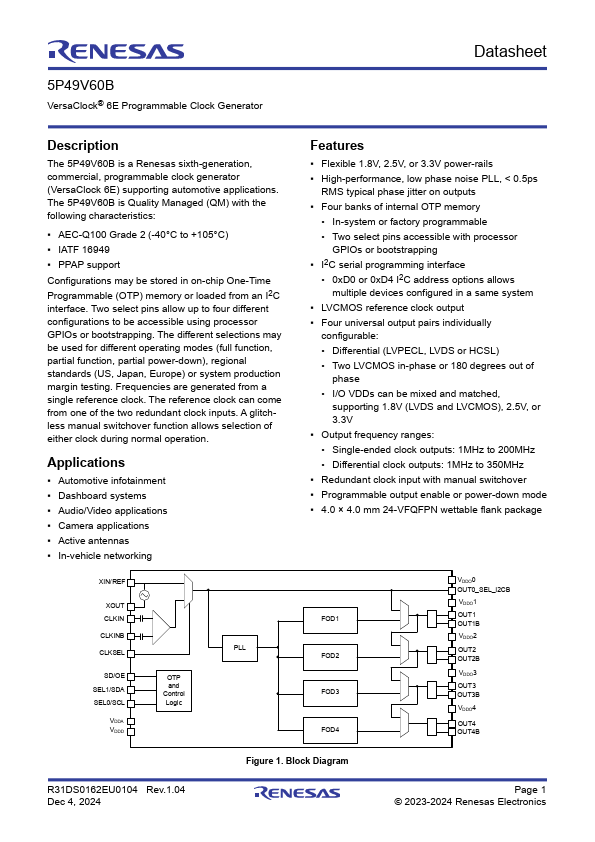

The 5P49V60B is a Renesas sixth-generation, mercial, programmable clock generator (VersaClock 6E) supporting automotive applications.

Key Features

- High-performance, low phase noise PLL, < 0.5ps

- Four banks of internal OTP memory

- In-system or factory programmable

- Two select pins accessible with processor

- I2C serial programming interface

- 0xD0 or 0xD4 I2C address options allows multiple devices configured in a same system

- LVCMOS reference clock output

- Four universal output pairs individually

- Differential (LVPECL, LVDS or HCSL)

- Two LVCMOS in-phase or 180 degrees out of

Applications

- Automotive infotainment