70V261S

Features

- True Dual-Ported memory cells which allow simultaneous access of the same memory location

- High-speed access

- mercial: 25/35ns (max.)

- Industrial: 25ns (max.)

- Low-power operation

- IDT70V261S Active: 300m W (typ.) Standby: 3.3m W (typ.)

- IDT70V261L Active: 300m W (typ.) Standby: 660μW (typ.)

- Separate upper-byte and lower-byte control for multiplexed bus patibility

- IDT70V261 easily expands data bus width to 32 bits or more using the Master/Slave select when cascading more than one device

- M/S = VIH for BUSY output flag on Master M/S = VIL for BUSY input on Slave

- Interrupt Flag

- On-chip port arbitration logic

- Full on-chip hardware support of semaphore signaling between ports

- Fully asynchronous operation from either port

- TTL-patible, single 3.3V (±0.3V) power supply

- Available in a 100-pin TQFP, Thin Quad Plastic Flatpack

- Industrial temperature range (-40°C to +85°C) is available for selected speed

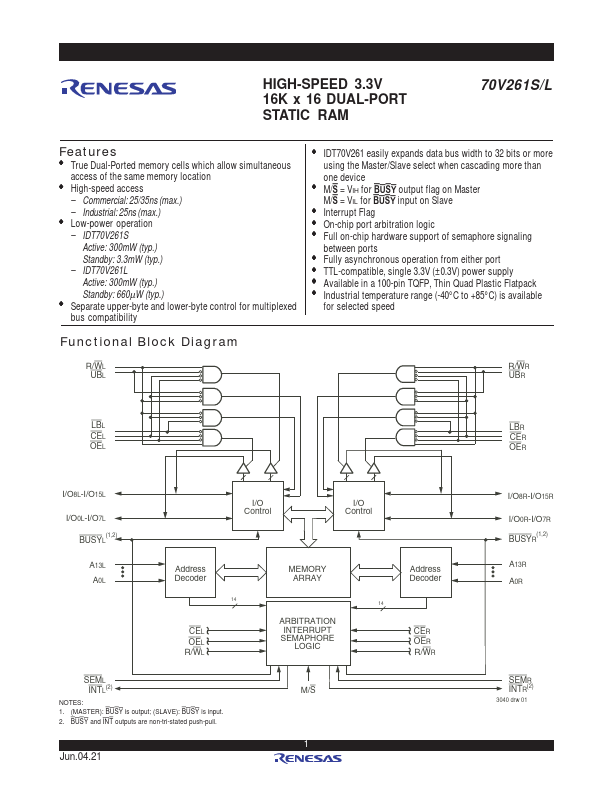

Functional Block Diagram

R/WL UBL

R/WR UBR

LBL CEL OEL

LBR CER

I/O8L-I/O15L

I/O0L-I/O7L BUSYL(1,2)

A13L A0L

I/O Control

I/O Control

Address Decoder

MEMORY ARRAY

14 14

CEL OEL R/WL

ARBITRATION INTERRUPT SEMAPHORE LOGIC

SEML INTL(2)

M/S

NOTE...