71V2556SA

71V2556SA is 3.3V Synchronous SRAMs manufactured by Renesas.

- Part of the 71V2556S comparator family.

- Part of the 71V2556S comparator family.

Features

- 128K x 36 memory configurations

- Supports high performance system speed

- 166 MHz

(3.5 ns Clock-to-Data Access)

- ZBTTM Feature

- No dead cycles between write and read cycles

- Internally synchronized output buffer enable eliminates the need to control OE

- Single R/W (READ/WRITE) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined applications

- 4-word burst capability (interleaved or linear)

- Individual byte write (BW1

- BW4) control (May tie active)

- Three chip enables for simple depth expansion

- 3.3V power supply (±5%), 2.5V I/O Supply (VDDQ)

- Optional

- Boundary Scan JTAG Interface (IEEE 1149.1 plaint)

- Packaged in a JEDEC standard 100-pin plastic thin quad flatpack (TQFP) and 119 ball grid array (BGA)

- Industrial temperature range (- 40°C to +85°C) is available for selected speeds

- Green parts available, see ordering information

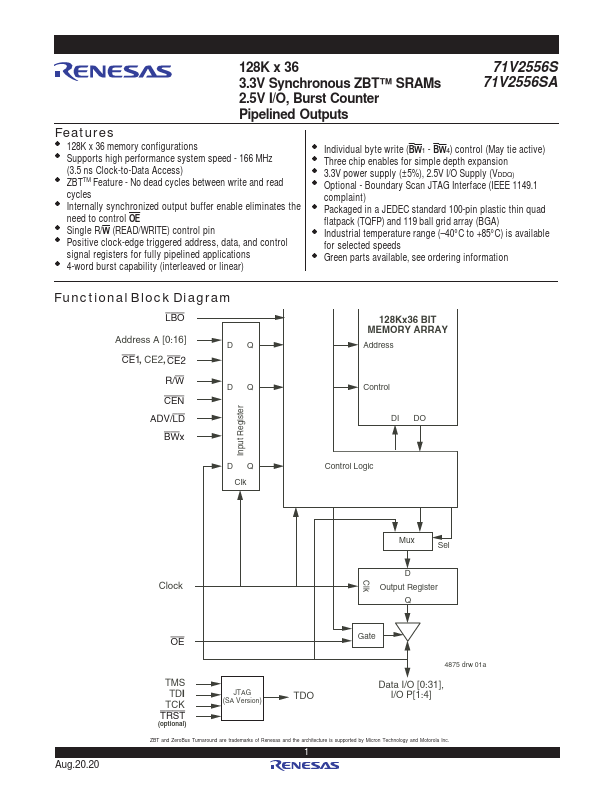

Functional Block Diagram

Address A [0:16] CE1, CE2, CE2 R/W CEN ADV/LD BWx

DQ DQ

128Kx36 BIT MEMORY ARRAY

Address

Control

DI DO

Input Register

DQ Clk

Control Logic

Aug.20.20

Clock

Clk

Mux

Sel

D Output Register

Gate...