74FCT38075S Overview

Key Specifications

Package: SOIC

Mount Type: Surface Mount

Pins: 8

Operating Voltage: 1.8 V

Description

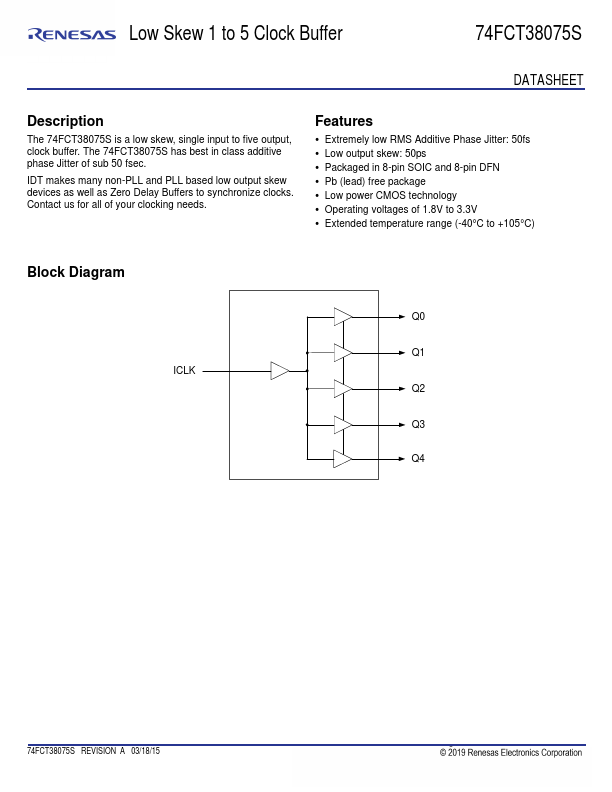

The 74FCT38075S is a low skew, single input to five output, clock buffer. The 74FCT38075S has best in class additive phase Jitter of sub 50 fsec.

Key Features

- Extremely low RMS Additive Phase Jitter: 50fs

- Low output skew: 50ps

- Packaged in 8-pin SOIC and 8-pin DFN

- Pb (lead) free package

- Low power CMOS technology