HD74HC390 Overview

Description

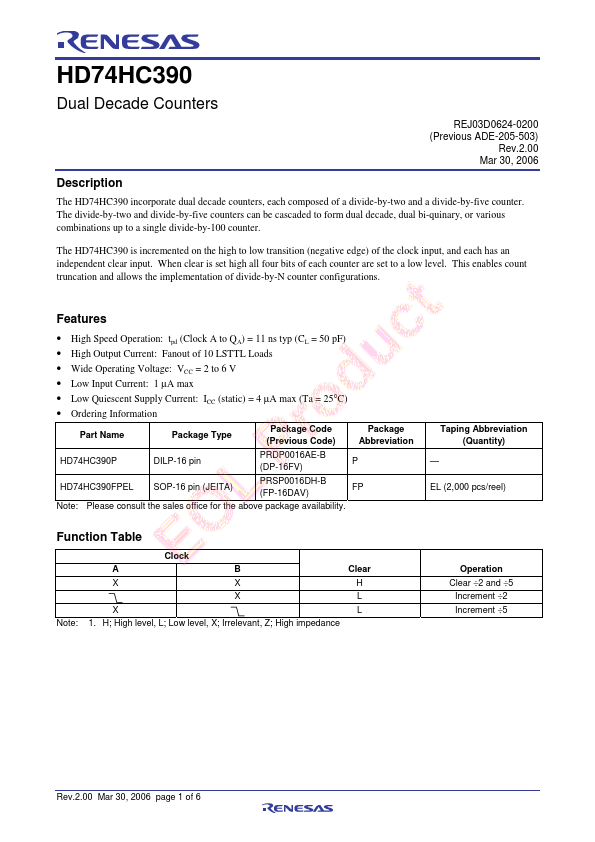

The HD74HC390 incorporate dual decade counters, each composed of a divide-by-two and a divide-by-five counter. The divide-by-two and divide-by-five counters can be cascaded to form dual decade, dual bi-quinary, or various combinations up to a single divide-by-100 counter.

Key Features

- High Speed Operation: tpd (Clock A to QA) = 11 ns typ (CL = 50 pF)

- High Output Current: Fanout of 10 LSTTL Loads

- Wide Operating Voltage: VCC = 2 to 6 V

- Low Input Current: 1 µA max

- Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C)