ICS9DB108 Overview

Description

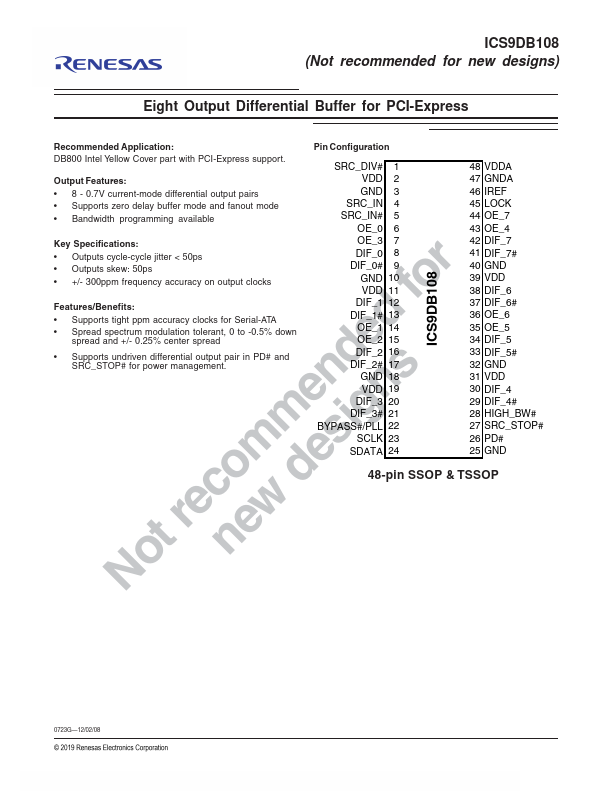

IN PWR PWR IN IN IN IN OUT OUT PWR PWR OUT OUT IN IN OUT OUT PWR PWR OUT OUT IN IN I/O Active low Input for determining SRC output frequency SRC or SRC/2. 0 = SRC/2, 1= SRC Power supply, nominal 3.3V Ground pin.

Key Features

- 8 - 0.7V current-mode differential output pairs

- Supports zero delay buffer mode and fanout mode

- Bandwidth programming available VDD GND SRC_IN SRC_IN# OE_0 2 3 4 5 6 47 GNDA 46 IREF 45 LOCK 44 OE_7 43 OE_4 Key Specifications

- Outputs cycle-cycle jitter < 50ps r

- Outputs skew: 50ps

- +/- 300ppm frequency accuracy on output clocks foFeatures/Benefits

- Supports tight ppm accuracy clocks for Serial-ATA d

- Spread spectrum modulation tolerant, 0 to -0.5% down spread and +/- 0.25% center spread e