IDT2305B Overview

Description

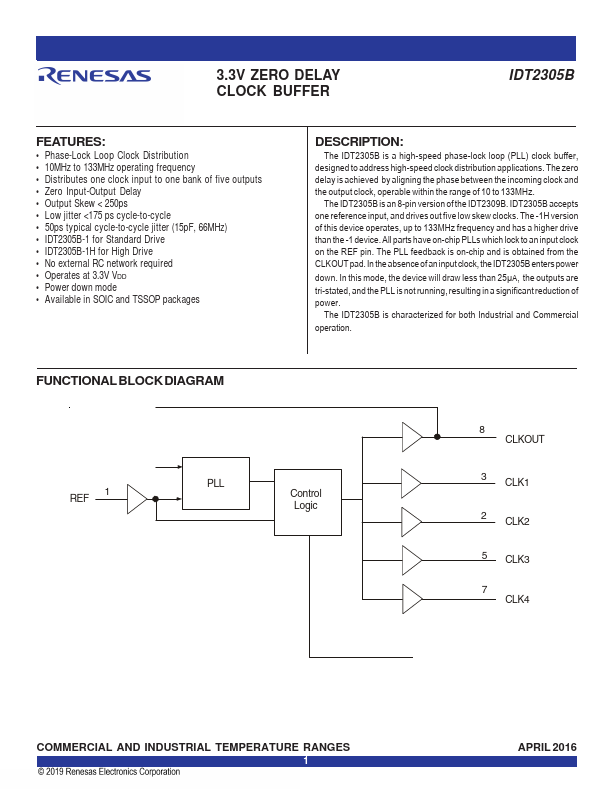

The IDT2305B is a high-speed phase-lock loop (PLL) clock buffer, designed to address high-speed clock distribution applications. The zero delay is achieved by aligning the phase between the incoming clock and the output clock, operable within the range of 10 to 133MHz.

Key Features

- Phase-Lock Loop Clock Distribution

- 10MHz to 133MHz operating frequency

- Distributes one clock input to one bank of five outputs

- Zero Input-Output Delay

- Output Skew < 250ps

- Low jitter <175 ps cycle-to-cycle

- 50ps typical cycle-to-cycle jitter (15pF, 66MHz)

- IDT2305B-1 for Standard Drive

- IDT2305B-1H for High Drive

- No external RC network required