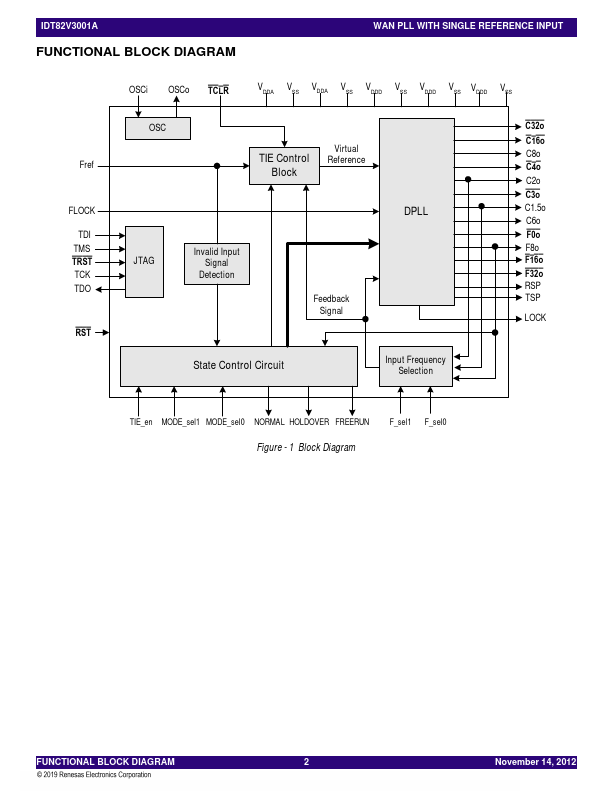

Datasheet Summary

WAN PLL WITH SINGLE REFERENCE INPUT

Features

- Supports AT&T TR62411 and Telcordia GR-1244-CORE Stratum 4 Enhanced and Stratum 4 timing for DS1 interfaces

- Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timingfor E1 interface

- Selectable input reference signal: 8 kHz, 1.544 MHz or 2.048 MHz

- Provides eight types of clock signals: C1.5o, C3o, C2o, C4o, C6o, C8o, C16o and C32o

- Provides six types of 8 kHz framing pulses: F0o, F8o, F16o, F32o, RSP and TSP

- Holdover frequency accuracy of 0.025 ppm

- Phase slope of 5 ns/125 µs

- Attenuates wander from 2.1 Hz

- Fast Lock mode

- Provides Time Interval Error (TIE) correction

- MTIE of 600 ns

- JTAG boundary scan

-...