M6MGB321S8TP

Description

M6MGB/T321S8TP provides for Software Lock Release function. Usually, all memory blocks are locked and can not be programed or erased, when F-WP# is low.

Key Features

- DINOR (Divided bit-line NOR) architecture for the memory cell

- M6MGB/T321S8TP is suitable for the application of the mobile-munication-system to reduce both the mount space and weight

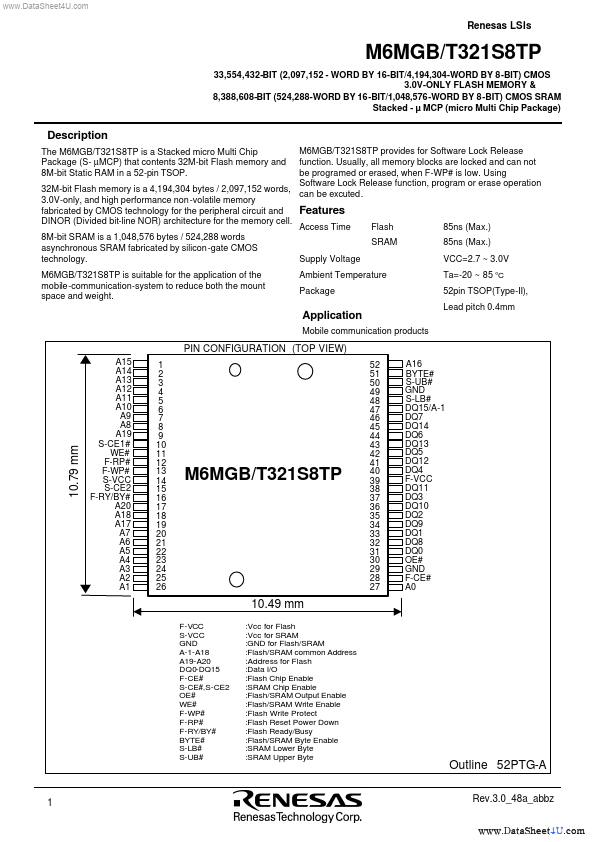

- Ambient Temperature Package Ta=-20 ~ 85 °C 52pin TSOP(Type-II), Lead pitch 0.4mm