MC100ES6056

Overview

- 360 ps Typical Propagation Delays

- Maximum Frequency > 3 GHz Typical

- PECL Mode Operating Range: VCC = 2.375 V to 3.8 V with VEE = 0 V

- ECL Mode Operating Range: VCC = 0 V with VEE = -2.375 V to -3.8 V

- Open Input Default State

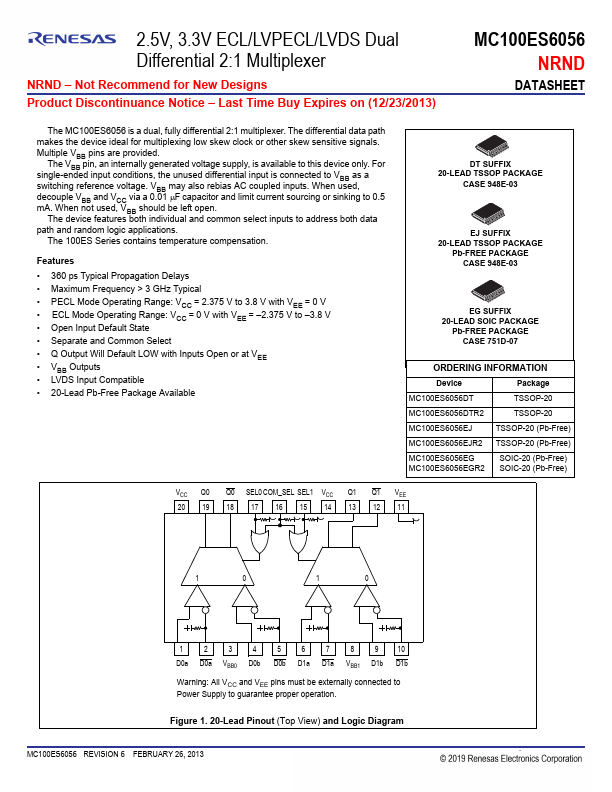

- Separate and Common Select

- Q Output Will Default LOW with Inputs Open or at VEE

- VBB Outputs

- LVDS Input Compatible

- 20-Lead Pb-Free Package Available