R5F52106ADFF

R5F52106ADFF is 50-MHz 32-bit RX MCUs manufactured by Renesas.

- Part of the R5F52108ADFP comparator family.

- Part of the R5F52108ADFP comparator family.

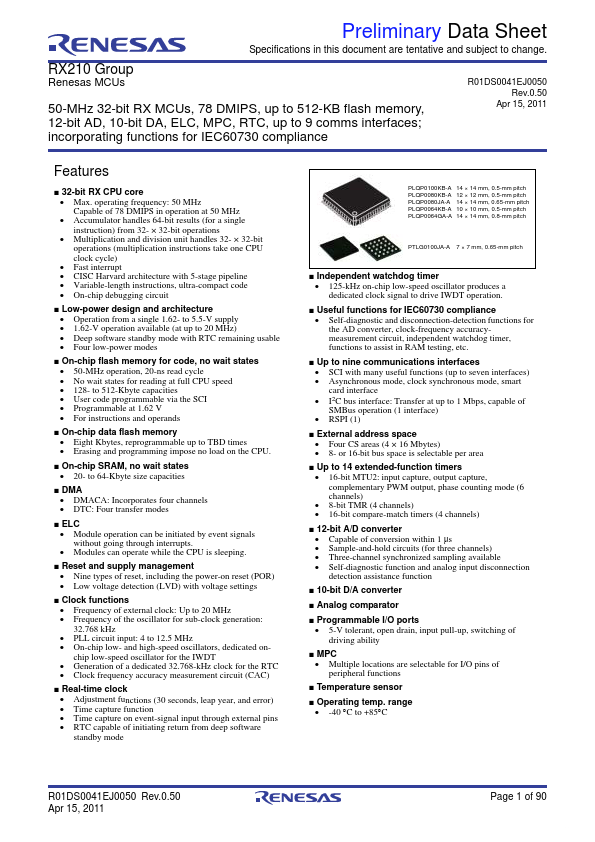

Preliminary Data Sheet

Specifications in this document are tentative and subject to change.

RX210 Group

Renesas MCUs

50-MHz 32-bit RX MCUs, 78 DMIPS, up to 512-KB flash memory, 12-bit AD, 10-bit DA, ELC, MPC, RTC, up to 9 ms interfaces; incorporating functions for IEC60730 pliance

R01DS0041EJ0050 Rev.0.50 Apr 15, 2011

Features

- 32-bit RX CPU core

- Max. operating frequency: 50 MHz Capable of 78 DMIPS in operation at 50 MHz

- Accumulator handles 64-bit results (for a single instruction) from 32- × 32-bit operations

- Multiplication and division unit handles 32- × 32-bit operations (multiplication instructions take one CPU clock cycle)

- Fast interrupt

- CISC Harvard architecture...