R5F571MLCDFC

R5F571MLCDFC is 240-MHz 32-bit RX MCU manufactured by Renesas.

- Part of the R5F571 comparator family.

- Part of the R5F571 comparator family.

Features

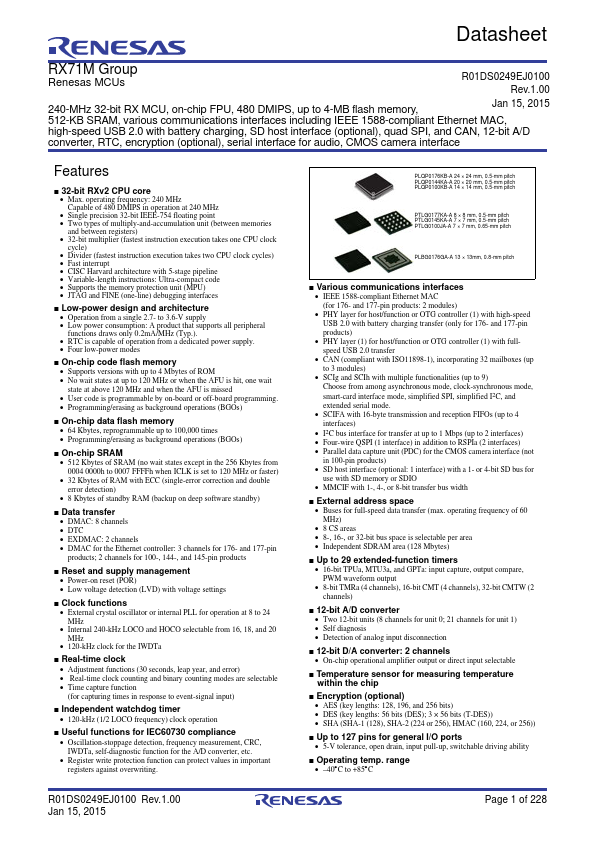

RX71M Group

Renesas MCUs

R01DS0249EJ0100 Rev.1.00

240-MHz 32-bit RX MCU, on-chip FPU, 480 DMIPS, up to 4-MB flash memory,

Jan 15, 2015

512-KB SRAM, various munications interfaces including IEEE 1588-pliant Ethernet MAC, high-speed USB 2.0 with battery charging, SD host interface (optional), quad SPI, and CAN, 12-bit A/D converter, RTC, encryption (optional), serial interface for audio, CMOS camera interface

Features

- 32-bit RXv2 CPU core

- Max. operating frequency: 240 MHz Capable of 480 DMIPS in operation at 240 MHz

- Single precision 32-bit IEEE-754 floating point

- Two types of multiply-and-accumulation unit (between memories and between registers)

-...