R5F572NDHDBD Overview

Key Specifications

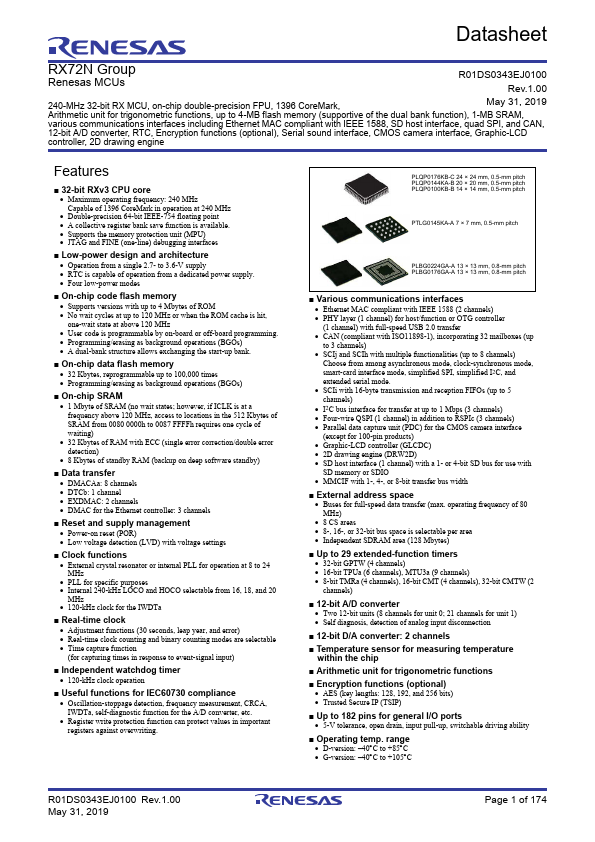

Package: LFBGA

Mount Type: Surface Mount

Pins: 224

Max Voltage (typical range): 3.6 V

Key Features

- 32-bit RXv3 CPU core

- Maximum operating frequency: 240 MHz Capable of 1396 CoreMark in operation at 240 MHz

- Double-precision 64-bit IEEE-754 floating point

- A collective register bank save function is available

- Supports the memory protection unit (MPU)