R7FS128782A01CLM Description

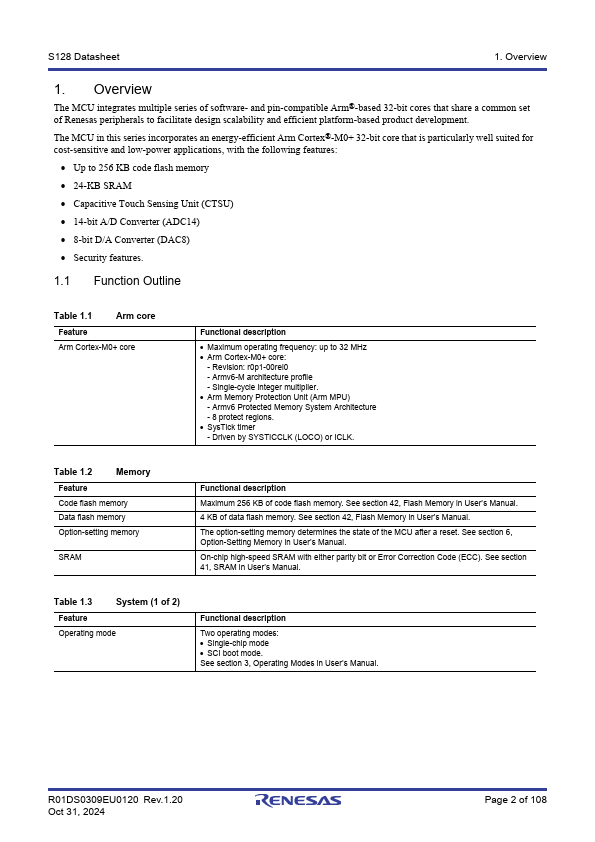

Datasheet S128 Microcontroller Group Datasheet R01DS0309EU0120 Rev.1.20 Oct 31, 2024 Ultra low power 32-MHz Arm® Cortex®-M0+ core, up to 256-KB code flash memory, 24-KB SRAM, Digital Addressable Lighting Interface, Capacitive Touch Sensing Unit, 14-bit A/D.

R7FS128782A01CLM Key Features

- Arm Cortex-M0+ Core

- Arm®v6-M architecture

- Maximum operating frequency: 32 MHz

- Arm® Memory Protection Unit (Arm MPU) with 8 regions

- Debug and Trace: DWT, BPU, CoreSight™ MTB-M0+

- CoreSight Debug Port: SW-DP

- Memory

- Up to 256-KB code flash memory

- 4-KB data flash memory (100,000 erase/write cycles)

- Up to 24-KB SRAM