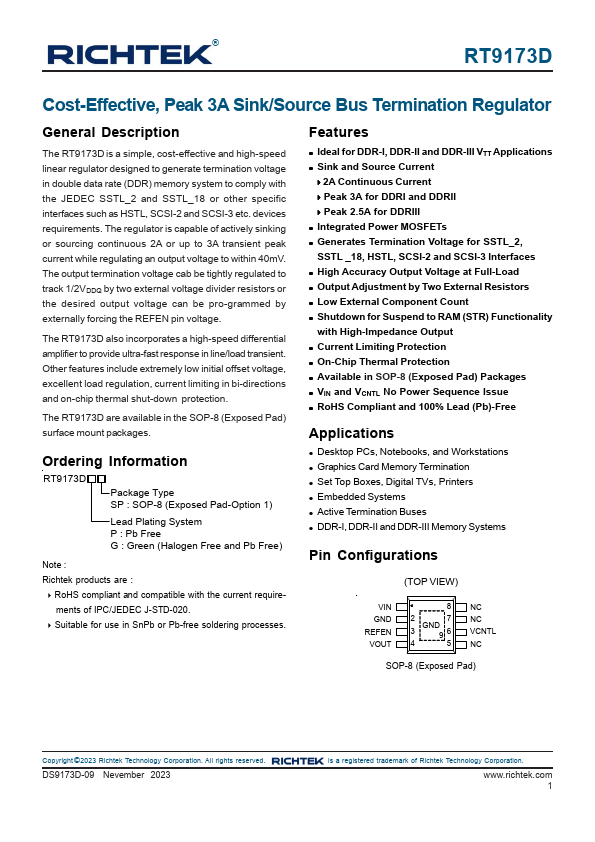

Datasheet Summary

®

Cost-Effective, Peak 3A Sink/Source Bus Termination Regulator

General Description

The RT9173D is a simple, cost-effective and high-speed linear regulator designed to generate termination voltage in double data rate (DDR) memory system to ply with the JEDEC SSTL_2 and SSTL_18 or other specific interfaces such as HSTL, SCSI-2 and SCSI-3 etc. devices requirements. The regulator is capable of actively sinking or sourcing continuous 2A or up to 3A transient peak current while regulating an output voltage to within 40mV. The output termination voltage cab be tightly regulated to track 1/2VDDQ by two external voltage divider resistors or the desired output voltage can be...