Datasheet Summary

..

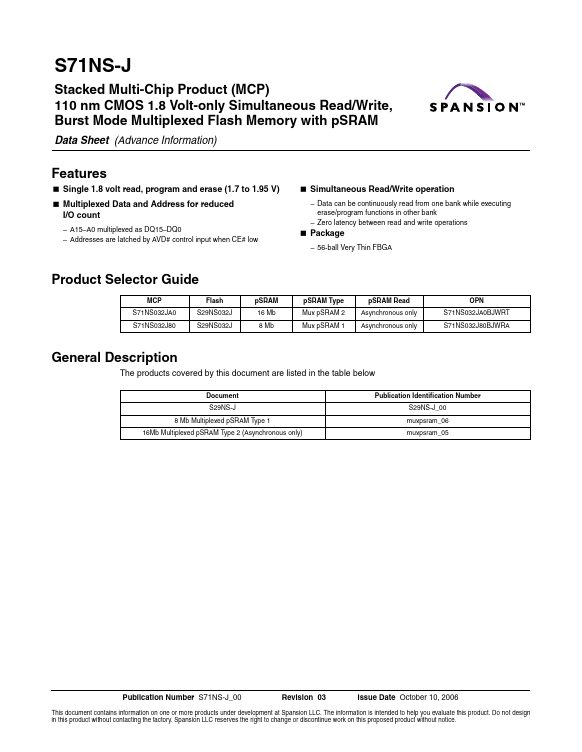

S71NS-J

Stacked Multi-Chip Product (MCP) 110 nm CMOS 1.8 Volt-only Simultaneous Read/Write, Burst Mode Multiplexed Flash Memory with pSRAM

S71NS-J Cover Sheet

Data Sheet (Advance Information)

Notice to Readers: This document states the current technical specifications regarding the Spansion product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See Notice On Data Sheet Designations for definitions.

Publication Number S71NS-J_00

Revision 03

Issue Date October 10, 2006

D a t a

S h e e t

( A d va n c e

I n fo r m a t i o n )

Notice On Data Sheet Designations

Spansion Inc. issues data...