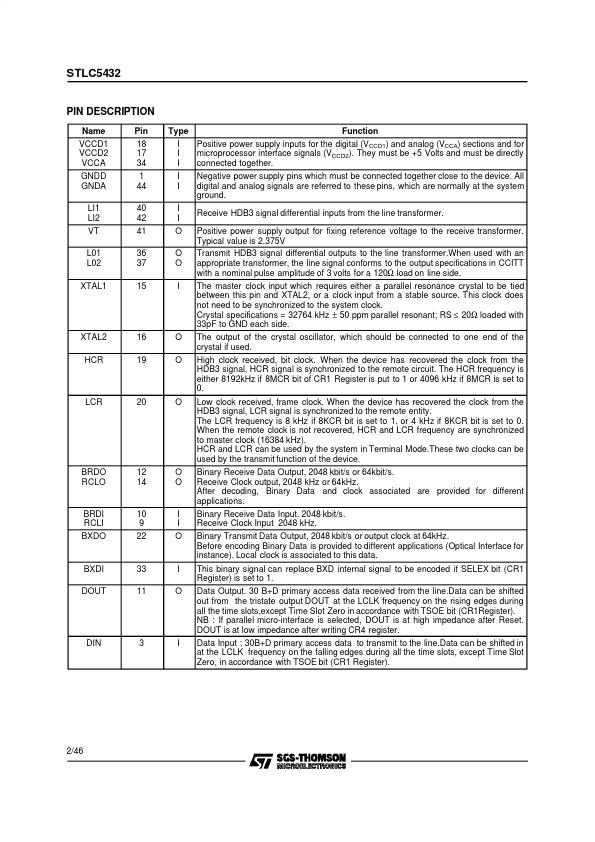

Datasheet Summary

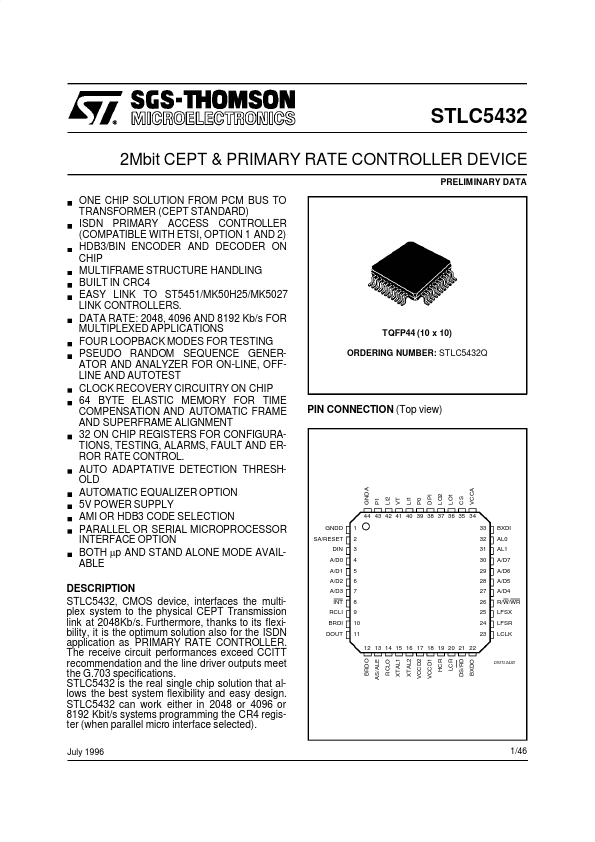

2Mbit CEPT & PRIMARY RATE CONTROLLER DEVICE

PRELIMINARY DATA

ONE CHIP SOLUTION FROM PCM BUS TO TRANSFORMER (CEPT STANDARD) ISDN PRIMARY ACCESS CONTROLLER (PATIBLE WITH ETSI, OPTION 1 AND 2) HDB3/BIN ENCODER AND DECODER ON CHIP MULTIFRAME STRUCTURE HANDLING BUILT IN CRC4 EASY LINK TO ST5451/MK50H25/MK5027 LINK CONTROLLERS. DATA RATE: 2048, 4096 AND 8192 Kb/s FOR MULTIPLEXED APPLICATIONS FOUR LOOPBACK MODES FOR TESTING PSEUDO RANDOM SEQUENCE GENERATOR AND ANALYZER FOR ON-LINE, OFFLINE AND AUTOTEST CLOCK RECOVERY CIRCUITRY ON CHIP 64 BYTE ELASTIC MEMORY FOR TIME PENSATION AND AUTOMATIC FRAME AND SUPERFRAME ALIGNMENT 32 ON CHIP REGISTERS FOR CONFIGURATIONS, TESTING, ALARMS,...