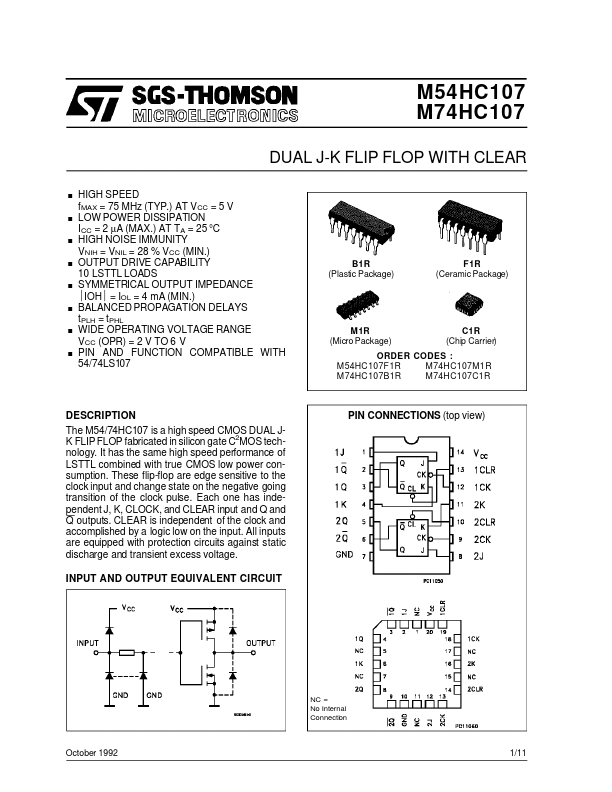

| Part | 74107 |

|---|---|

| Description | DUAL J-K FLIP-FLOP |

| Manufacturer | STMicroelectronics |

| Size | 248.85 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 7410 | National Semiconductor | Triple 3 Input NAND Gates |

| PC7410 | Atmel | PowerPC 7410 RISC Microprocessor |

| ACMD-7410 | Avago Technologies | UMTS/NCDMA/Co-band GSM Rx Band 2 Duplexer |

| 74109 | Texas Instruments | Dual J-K Positive-Edge-Triggered Flip-Flops |

| WED3C7410E16M-XBHX | White Electronic Designs | 7410E RISC Microprocessor |