WED3C7410E16M-XBHX

WED3C7410E16M-XBHX is 7410E RISC Microprocessor manufactured by White Electronic Designs.

atures: doze, nap, sleep and dynamic power management. The WED3C7410E16M-XBHX multichip package consists of: 7410E Alti Vec™ RISC processor Dedicated 2MB SSRAM L2 cache, configured as 256Kx72 21mmx25mm, 255 Hi TCE™ Ball Grid Array (CBGA) Core frequency = 450 or 400MHz @ 1.8V Maximum L2 Cache frequency = 200MHz Maximum 60x Bus frequency = 100MHz

- This product is under development, is not qualified or characterized and is subject to change without notice.

The WED3C7410E16M-XBHX is offered in mercial (0°C to +70°C), industrial (-40°C to +85°C) and military (-55°C to +125°C) temperature ranges and is well suited for embedded applications such as missiles, aerospace, flight puters, fire control systems and rugged critical systems.

Features

Footprint patible with WED3C7410E16M-XBX, WED3C7558M-XBX and WED3C750A8M-200BX Implementation of Altivec™ technology instruction set Optional, high-bandwidth MPX bus interface Hi TCE™ interposer for TCE patibility to laminate substrates for increased Board level reliability Available with eutectic or high lead solder balls

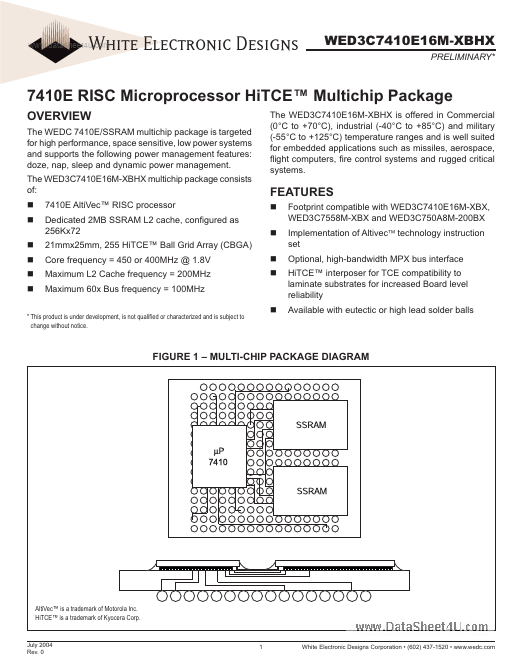

FIGURE 1

- MULTI-CHIP PACKAGE DIAGRAM

Alti Vec™ is a trademark of Motorola Inc. Hi TCE™ is a trademark of Kyocera Corp.

July 2004 Rev. 0

White Electronic Designs Corporation

- (602) 437-1520

- .wedc.

July 2004 Rev. 0

Instruction MMU SRs (Shadow) 128-Entry DTLB Tags Data MMU

..

Fetcher BTIC (64 Entry) LR SRs (Original) 128-Entry DTLB DBAT Array Tags CTR BHT (512 Entry) IBAT Array 32-Kbyte I Cache

Branch Processing Unit

128-Bit (4 Instructions)

Additional Features

Time Base Counter/Decrementer Clock Muliplier JTAG/COP Interface Thermal/Power Management Performance Monitor Instruction Queue (6 Word) Dispatch Unit

32-Kbyte I Cache

Reservation Station Reservation Station Reservation Station GPR File 6 Rename Buffers + Load/Store Unit Interger Unit 1 System Register Unit Interger Unit 2 VR File 6 Rename Buffers Reservation Station

Reservation Station

Reservation Station (2 Entry) FPR File 6 Rename...