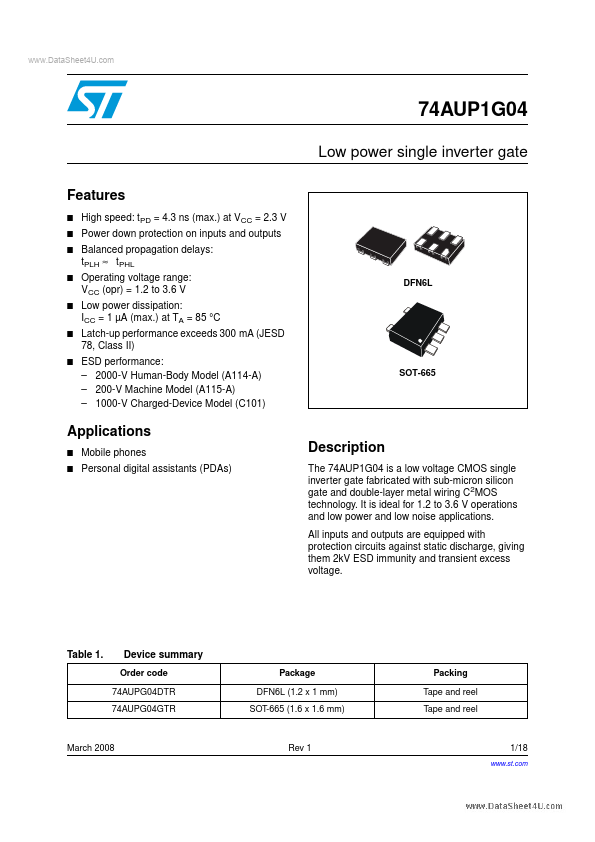

| Part | 74AUP1G04 |

|---|---|

| Description | Low power single inverter gate |

| Manufacturer | STMicroelectronics |

| Size | 438.20 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74AUP1G04 | Nexperia | Low-power inverter |

| 74AUP1G04-Q100 | Nexperia | Low-power inverter |

| 74AUP1G04 | NXP Semiconductors | Low-power inverter |

| 74AUP1G04 | Diodes Incorporated | SINGLE INVERTER GATE |

| 74AUP1G06 | NXP Semiconductors | Low-power inverter |