74HCT74

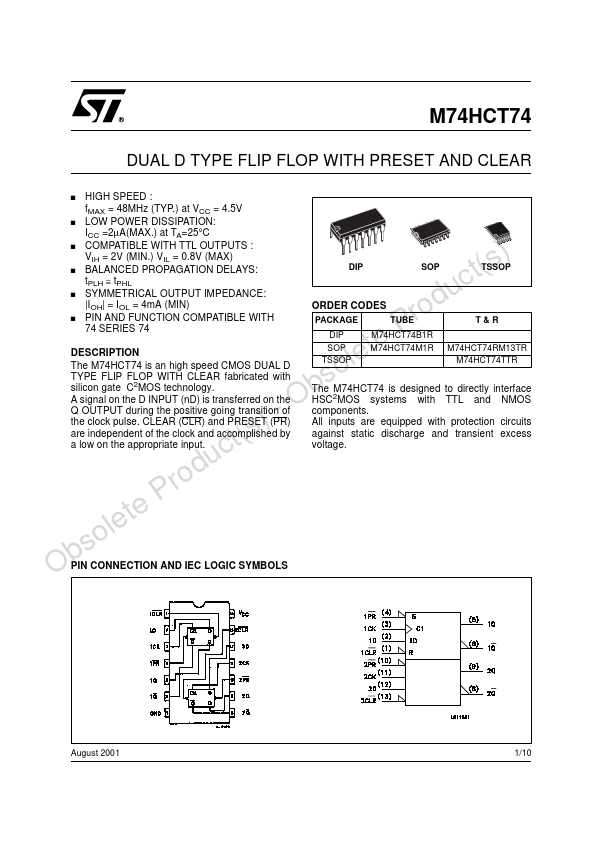

DESCRIPTION

PIN No

SYMBOL NAME AND FUNCTION

1,13

1CLR, 2CLR

Asynchronous Reset Direct Input

2, 12

1D, 2D Data Inputs

3, 11

Clock Input 1CK, 2CK (LOW-to-HIGH,

Edge-Triggered)

4, 10

1PR, 2PR

Asynchronous Set

- Direct Input

5, 9 1Q, 2Q True Flip-Flop Outputs duct(s)TRUTH TABLE

Pro CLR lete L

H so L b H

- OH )H t(s X : Don’t Care

INPUTS

PR D HX LX LX HL

HH HX

Obsolete Produc LOGIC DIAGRAM

6, 8

1Q, 2Q plement Flip-Flop Outputs

7 GND Ground (0V)

14 Vcc Positive Supply Voltage

OUTPUTS

CK Q

XL XH XH

HL Qn Qn

FUNCTION

CLEAR PRESET

---------NO CHANGE

This logic diagram has not be used to estimate propagation delays

2/10

M74HCT74

ABSOLUTE MAXIMUM...