74VHC125

Description

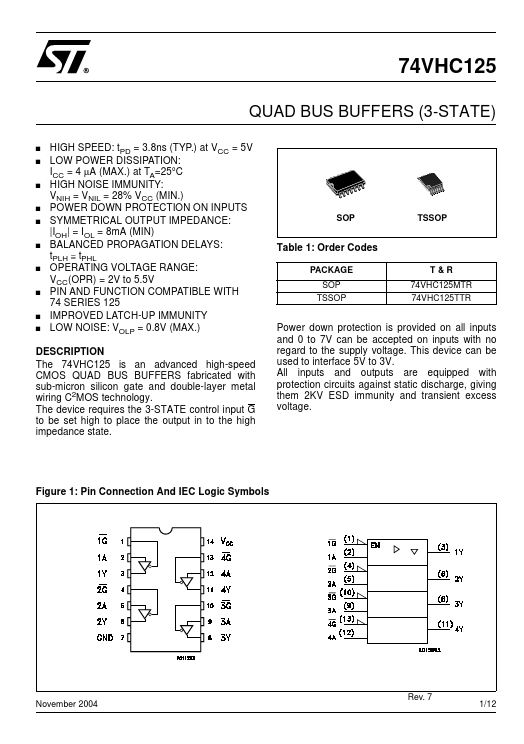

The 74VHC125 is an advanced high-speed CMOS QUAD BUS BUFFERS fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. The device requires the 3-STATE control input G to be set high to place the output in to the high impedance state.