Datasheet Summary

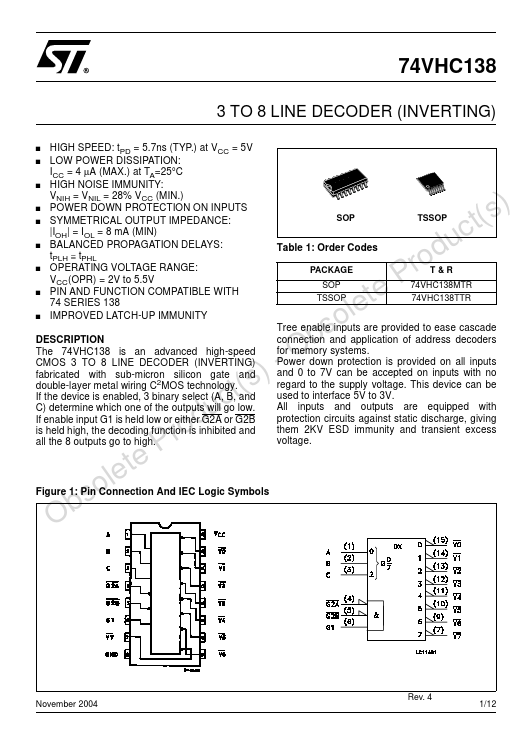

3 TO 8 LINE DECODER (INVERTING) s HIGH SPEED: tPD = 5.7ns (TYP.) at VCC = 5V s LOW POWER DISSIPATION:

ICC = 4 µA (MAX.) at TA=25°C s HIGH NOISE IMMUNITY:

VNIH = VNIL = 28% VCC (MIN.)

)s POWER DOWN PROTECTION ON INPUTS t(ss SYMMETRICAL OUTPUT IMPEDANCE: c|IOH| = IOL = 8 mA (MIN) us BALANCED PROPAGATION DELAYS: dtPLH ≅ tPHL ros OPERATING VOLTAGE RANGE: PVCC(OPR) = 2V to 5.5V s PIN AND FUNCTION PATIBLE WITH te74 SERIES 138 les IMPROVED LATCH-UP IMMUNITY bsoDESCRIPTION

The 74VHC138 is an advanced high-speed

- OCMOS 3 TO 8 LINE DECODER (INVERTING) )fabricated with sub-micron silicon gate and t(sdouble-layer metal wiring C2MOS technology.

If the device is enabled, 3 binary...