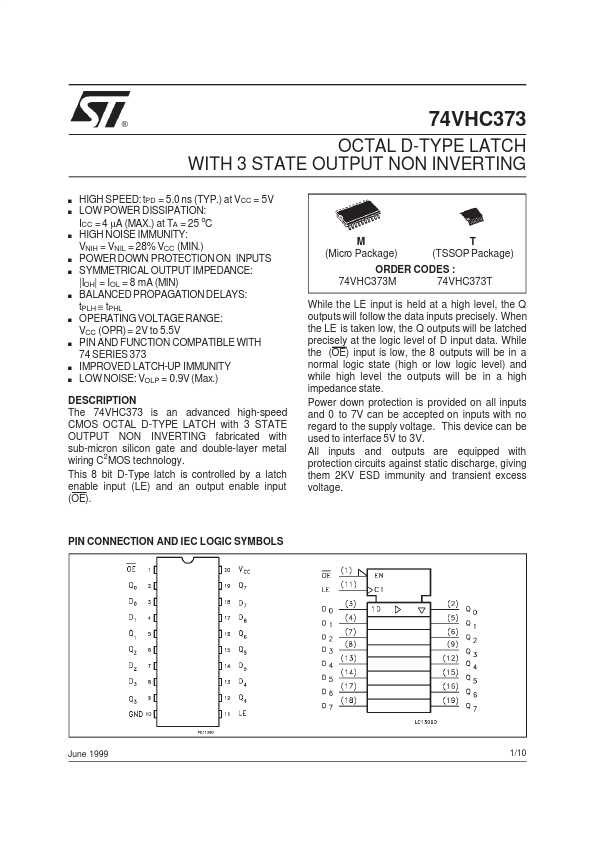

74VHC373 Description

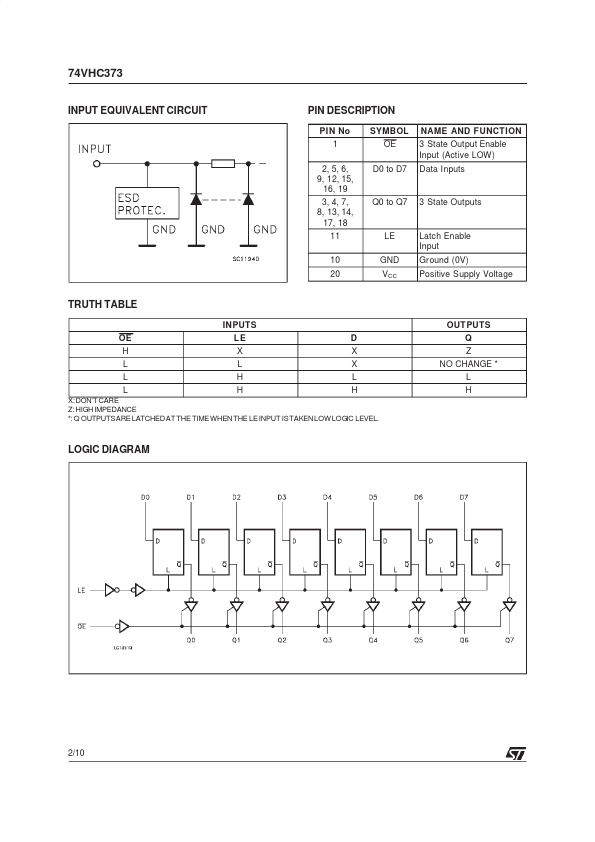

The 74VHC373 is an advanced high-speed CMOS OCTAL D-TYPE LATCH with 3 STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. This 8 bit D-Type latch is controlled by a latch enable input (LE) and an output enable input (OE). Q OUTPUTSARE LATCHED AT THE TIME WHEN THE LEINPUT ISTAKEN LOW LOGIC LEVEL.