74VHCT174A Overview

Description

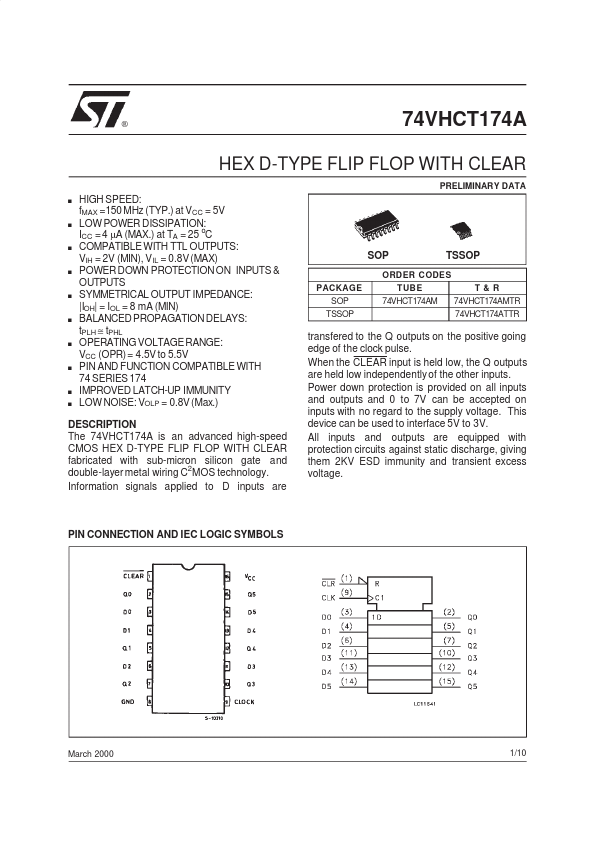

The 74VHCT174A is an advanced high-speed CMOS HEX D-TYPE FLIP FLOP WITH CLEAR fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. Information signals applied to D inputs are transfered to the Q outputs on the positive going edge of the clock pulse.