L55NH3LL

Key Features

- Improved die-to-footprint ratio c

- Very low profile package (1mm max) du

- Very low thermal resistance ro )

- Very low gate charge P t(s

- Low threshold device lete ducApplication so ro

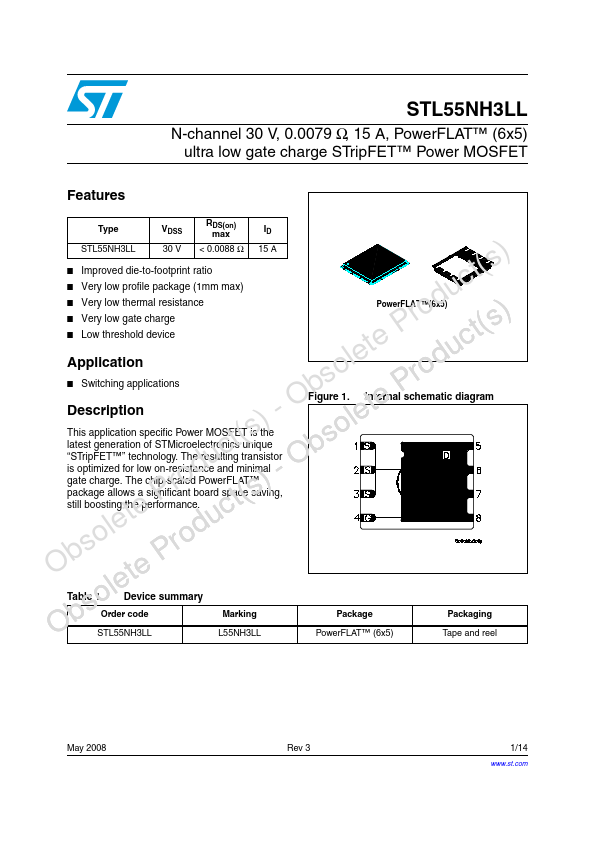

- Switching applications - Ob te PDescription t(s) oleThis application specific Power MOSFET is the slatest generation of STMicroelectronics unique c b“STripFET™” technology. The resulting transistor u Ois optimized for low on-resistance and minimal rod -gate charge. The chip-scaled PowerFLAT™ P t(s)package allows a significant board space saving, still boosting the performance. PowerFLAT™(6x5) Figure

- Internal schematic diagram Obsolleettee ProducTable

- Device summary soOrder code Ob STL55NH3LL Marking L55NH3LL Package PowerFLAT™ (6x5) Packaging Tape and reel May 2008 Rev 3 1/14