M48Z35Y

Features

- Integrated, ultra low power SRAM, power-fail control circuit, and battery

- READ cycle time equals WRITE cycle time

- Automatic power-fail chip deselect and WRITE protection

- WRITE protect voltages:

(VPFD = power-fail deselect voltage)

- M48Z35: VCC = 4.75 to 5.5 V;

4.5 V ≤ VPFD ≤ 4.75 V

- M48Z35Y: 4.5 to 5.5 V;

4.2 V ≤ VPFD ≤ 4.5 V

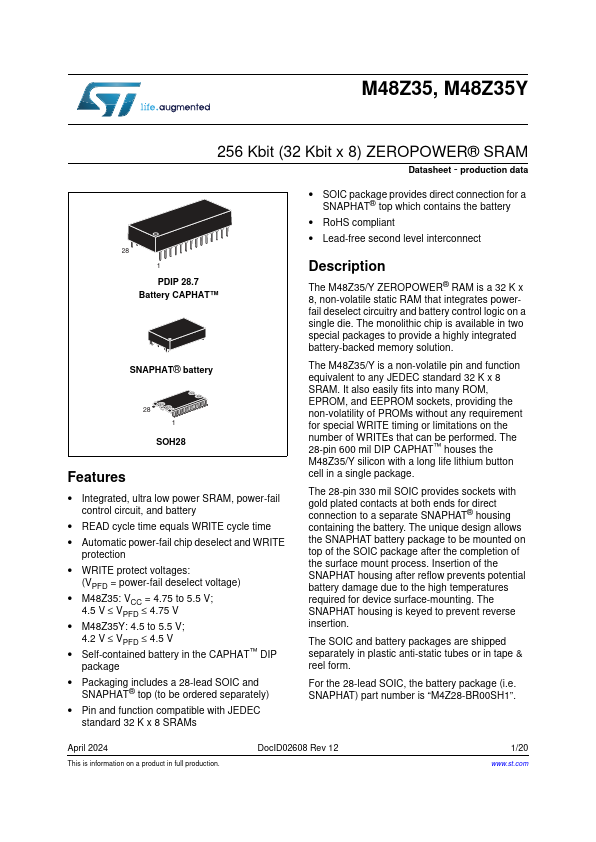

- Self-contained battery in the CAPHAT™ DIP package

- Packaging includes a 28-lead SOIC and

SNAPHAT® top (to be ordered separately)

- Pin and function patible with JEDEC standard 32 K x 8 SRAMs

- SOIC package provides direct connection for a SNAPHAT® top which contains the battery

- Ro HS pliant

- Lead-free second level interconnect

Description

The M48Z35/Y ZEROPOWER® RAM is a 32 K x 8, non-volatile static RAM that integrates powerfail deselect circuitry and battery control logic on a single die. The monolithic chip is available in two special packages to provide a highly integrated battery-backed memory solution.

The M48Z35/Y is a non-volatile...