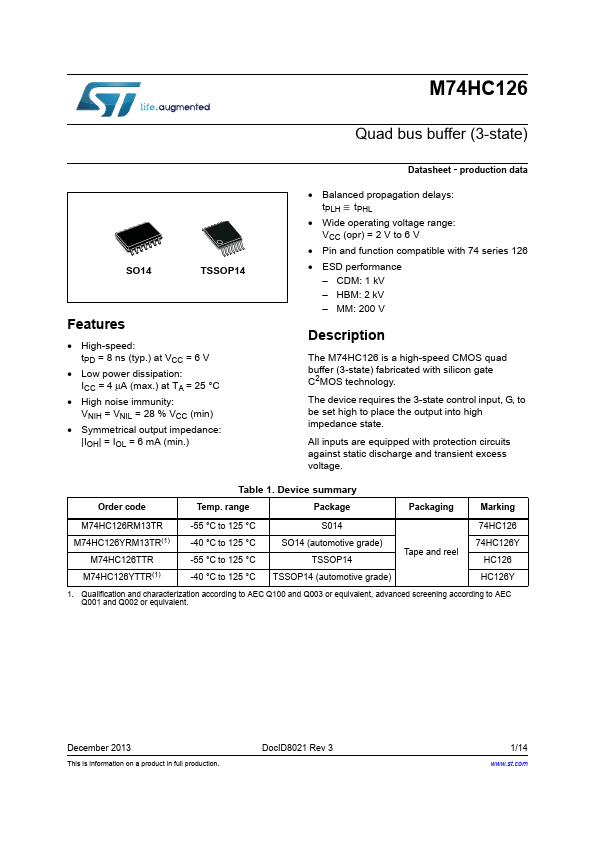

M74HC126

Description

The M74HC126 is a high-speed CMOS quad buffer (3-state) fabricated with silicon gate C2MOS technology. The device requires the 3-state control input, G, to be set high to place the output into high impedance state.

Key Features

- High-speed: tPD = 8 ns (typ.) at VCC = 6 V

- Low power dissipation: ICC = 4 μA (max.) at TA = 25 °C

- High noise immunity: VNIH = VNIL = 28 % VCC (min)

- Symmetrical output impedance: |IOH| = IOL = 6 mA (min.)

- Balanced propagation delays: tPLH ≅ tPHL

- Wide operating voltage range: VCC (opr) = 2 V to 6 V

- Pin and function compatible with 74 series 126

- ESD performance - CDM: 1 kV - HBM: 2 kV - MM: 200 V