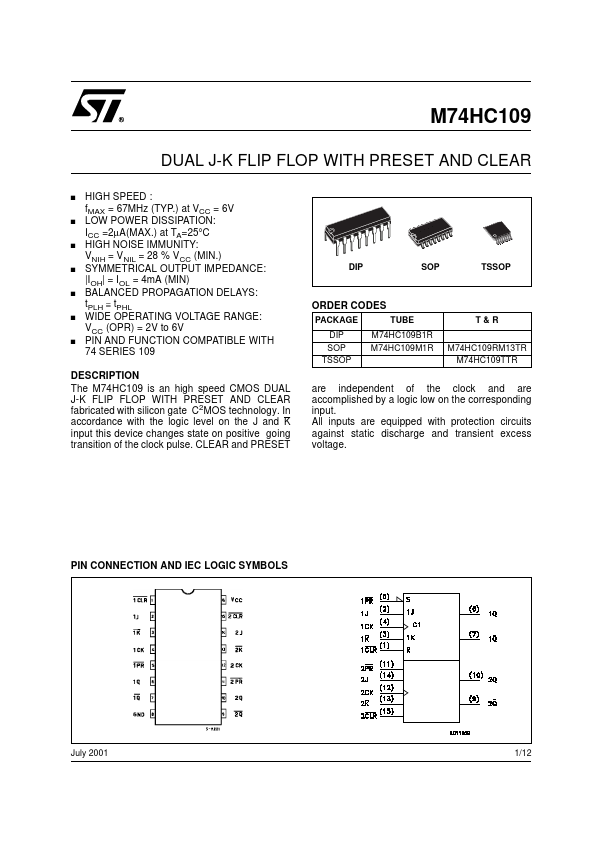

- Part: M74HC109

- Description: DUAL J-K FLIP FLOP

- Manufacturer: STMicroelectronics

- Size: 187.29 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| M74HC10 | STMicroelectronics | TRIPLE 3-INPUT NAND GATE |

| M74HC107 | STMicroelectronics | DUAL J-K FLIP FLOP |