SPC560P40L1 Overview

Key Specifications

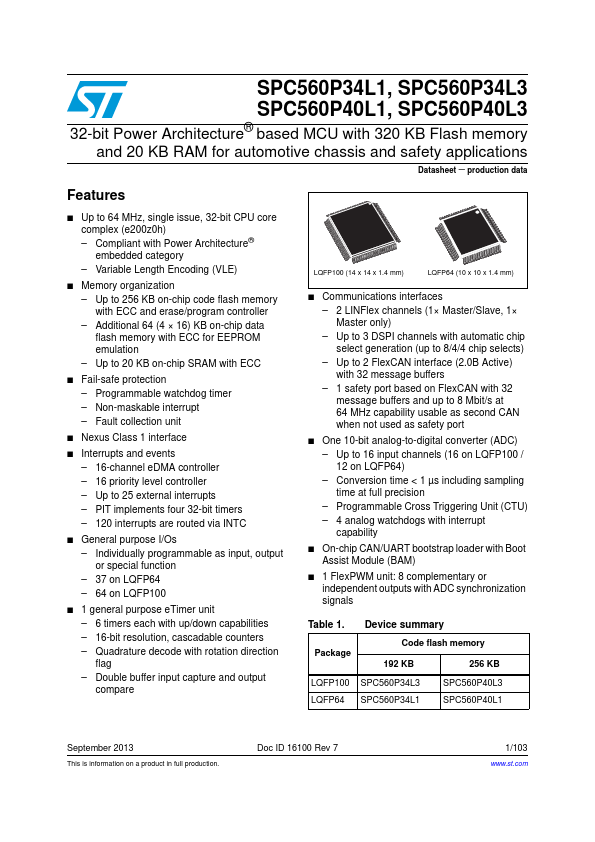

Package: LFQFP

Pins: 64

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Key Features

- Memory organization – Up to 256 KB on-chip code flash memory with ECC and erase/program controller – Additional 64 (4 ×

- KB on-chip data flash memory with ECC for EEPROM emulation – Up to 20 KB on-chip SRAM with ECC

- Fail-safe protection – Programmable watchdog timer – Non-maskable interrupt – Fault collection unit

- Nexus Class 1 interface

- General purpose I/Os – Individually programmable as input, output or special function – 37 on LQFP64 – 64 on LQFP100