SPC564A80L7 Overview

Key Specifications

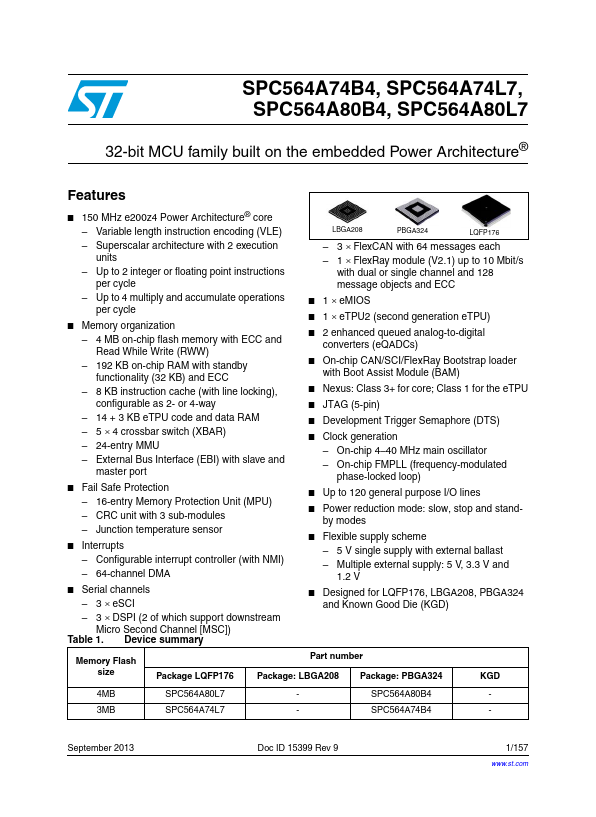

Package: LFQFP

Mount Type: Surface Mount

Pins: 176

Operating Voltage: 1.2 V

Key Features

- Fail Safe Protection – 16-entry Memory Protection Unit (MPU) – CRC unit with 3 sub-modules – Junction temperature sensor

- Interrupts – Configurable interrupt controller (with NMI) – 64-channel DMA

- Serial channels – 3 eSCI – 3 DSPI (2 of which support downstream Micro Second Channel [MSC]) Table

- 1 eTPU2 (second generation eTPU)

- 2 enhanced queued analog-to-digital converters (eQADCs)