ST22N144

ST22N144 is Smartcard 32-Bit RISC MCU manufactured by STMicroelectronics.

FEATURES

ADVANCED MEMORY PROTECTION

- -

- Memory Protection Unit for application firewalling and peripheral access control Domain switching securely controlled by protected Context Stack Native/Java, Code/Data memory attributes with 128-byte granularity Java stack with both 16 and 32-bit accesses User and Supervisor mode stacks Security Context Stack

32-BIT RISC CPU WITH 24-BIT LINEAR MEMORY ADDRESSING 368 KBYTES USER ROM 12 KBYTES USER RAM 144 KBYTES USER EEPROM DUAL INSTRUCTION SET, JAVACARD ™ AND NATIVE 4-STAGE PIPELINE 16 GENERAL PURPOSE 32-BIT REGISTERS, AND SPECIAL REGISTERS 4 MASKABLE INTERRUPT LEVELS SUPERVISOR AND USER MODES CPU SECURITY INSTRUCTIONS

- - Dedicated instructions for DES and Triple DES implementation Dedicated instructions (Multiply and Accumulate) for efficient implementation of modular arithmetic and elliptic curves based cryptosystems CRC instruction (ISO 3309 16-bit Checksum)

32-BIT RISC CPU

I I I I I

FOUR WORKING STACKS

- -

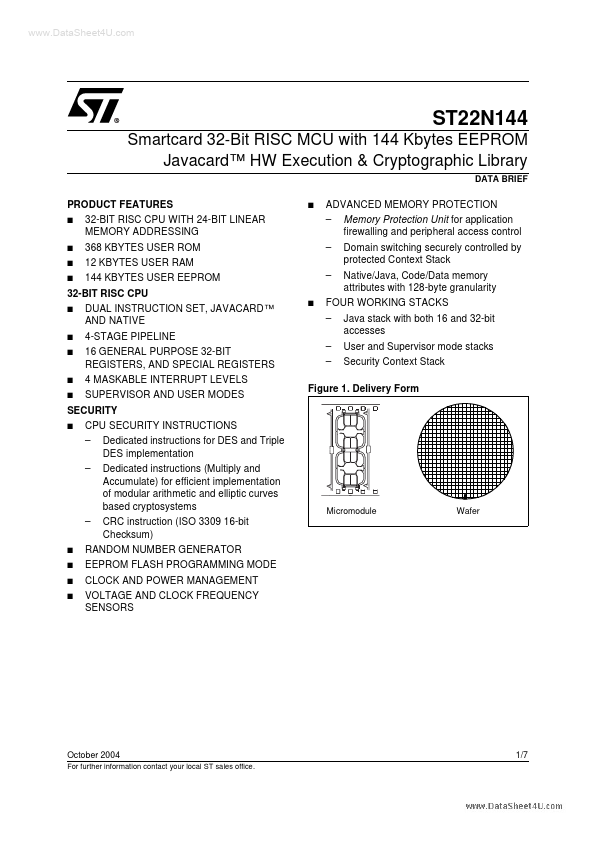

- Figure 1. Delivery Form

4 4

SECURITY

Micromodule

Wafer

- I I I I

RANDOM NUMBER GENERATOR EEPROM FLASH PROGRAMMING MODE CLOCK AND POWER MANAGEMENT VOLTAGE AND CLOCK FREQUENCY SENSORS

October 2004

For further information contact your local ST sales office.

1/7

..

CRYPTOGRAPHIC LIBRARY The Crypto Library is provided as a separate ROM area with an access through a unique entry point. This library provides optimized -for the Smart J core- and secured implementation of the following features

:

MEMORY

HIGHLY RELIABLE CMOS EEPROM TECHNOLOGY

- -

- Error Correction Code for single bit fail within a 32-bit word 10 years data retention, 500,000 Erase/ Write cycles endurance 1 to 128 bytes Erase or Program in 2 ms typical Dual memory buses for data and instruction Byte, Short (2) and Word (4) load and store Address auto-increment

ASYMMETRICAL ALGORITHMS

- -

- RSA signature/verification Prime number generation (up to 1024-bit) RSA key putation (up to 2048-bit) SHA-1

- -...