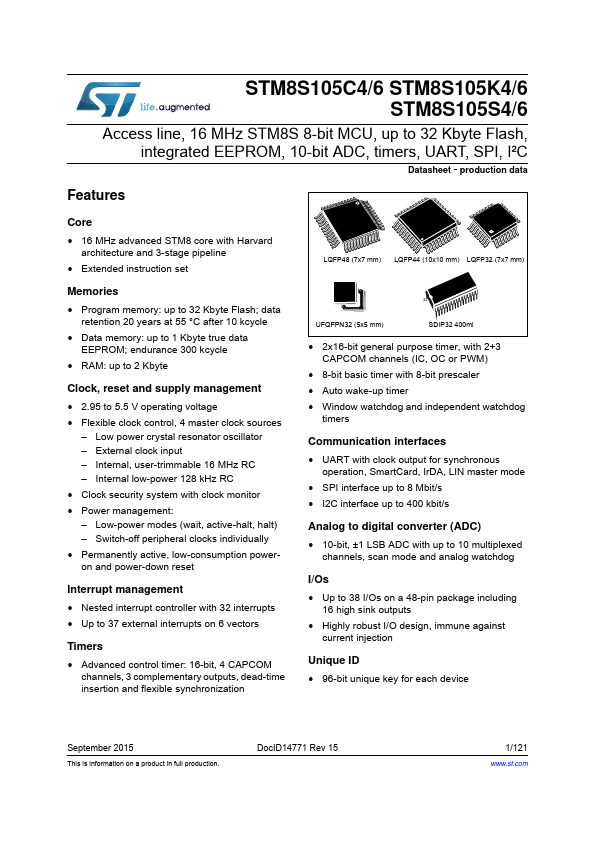

STM8S105K4

Key Features

- 16 MHz advanced STM8 core with Harvard architecture and 3-stage pipeline

- Extended instruction set Memories

- Program memory: up to 32 Kbyte Flash; data retention 20 years at 55 °C after 10 kcycle

- Data memory: up to 1 Kbyte true data EEPROM; endurance 300 kcycle

- RAM: up to 2 Kbyte Clock, reset and supply management

- 2.95 to 5.5 V operating voltage

- Flexible clock control, 4 master clock sources - Low power crystal resonator oscillator - External clock input - Internal, user-trimmable 16 MHz RC - Internal low-power 128 kHz RC

- Clock security system with clock monitor

- Power management: - Low-power modes (wait, active-halt, halt) - Switch-off peripheral clocks individually

- Permanently active, low-consumption poweron and power-down reset Interrupt ma