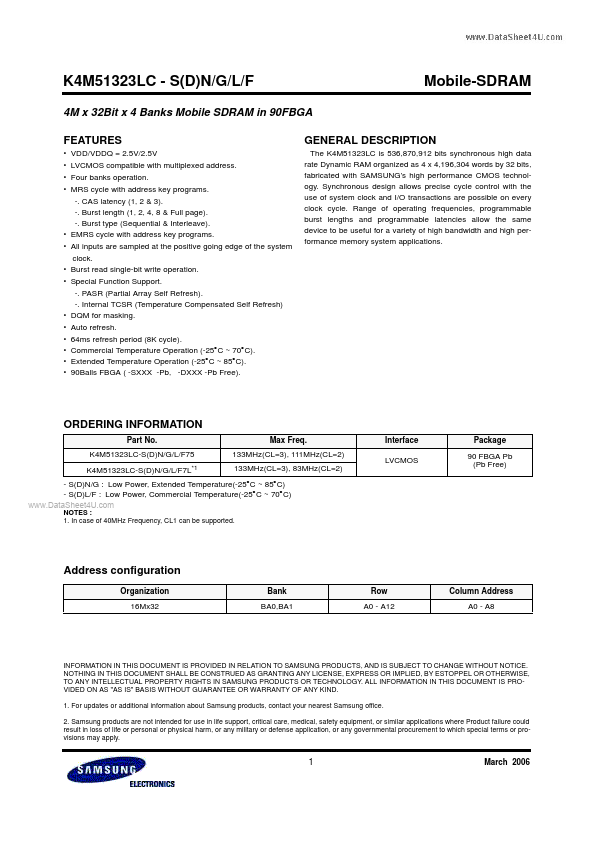

K4M51323LC-SDN

Description

The K4M51323LC is 536,870,912 bits synchronous high data rate Dynamic RAM organized as 4 x 4,196,304 words by 32 bits, fabricated with SAMSUNG’s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock and I/O transactions are possible on every clock cycle.

Key Features

- VDD/VDDQ = 2.5V/2.5V

- LVCMOS compatible with multiplexed address.

- Four banks operation.

- MRS cycle with address key programs. -. CAS latency (1, 2 & 3). -. Burst length (1, 2, 4, 8 & Full page). -. Burst type (Sequential & Interleave).

- EMRS cycle with address key programs.

- All inputs are sampled at the positive going edge of the system clock.

- Burst read single-bit write operation.

- Special Function Support. -. PASR (Partial Array Self Refresh). -. Internal TCSR (Temperature Compensated Self Refresh)

- DQM for masking.

- Auto refresh. * * *