Datasheet Summary

CMOS SDRAM

64Mbit SDRAM

1M x 16Bit x 4 Banks Synchronous DRAM LVTTL

Revision 0.1 Sept. 2001

- Samsung Electronics reserves the right to change products or specification without notice.

Rev.0.1 Sept. 2001

Revision History Revision 0.0 (June, 2001) Revision 0.1 (Sep., 2001)

- CMOS SDRAM

Changed the Notes in Operating AC Parameter. < Before > 5. For 1H/1L, tRDL=1CLK and tDAL=1CLK+tRP is also supported . SAMSUNG remends tRDL=2CLK and tDAL=2CLK + tRP. < After > 5.In 100MHz and below 100MHz operating conditions, tRDL=1CLK and tDAL=1CLK + 20ns is also supported. SAMSUNG remends tRDL=2CLK and tDAL=2CLK + tRP.

Rev.0.1 Sept. 2001

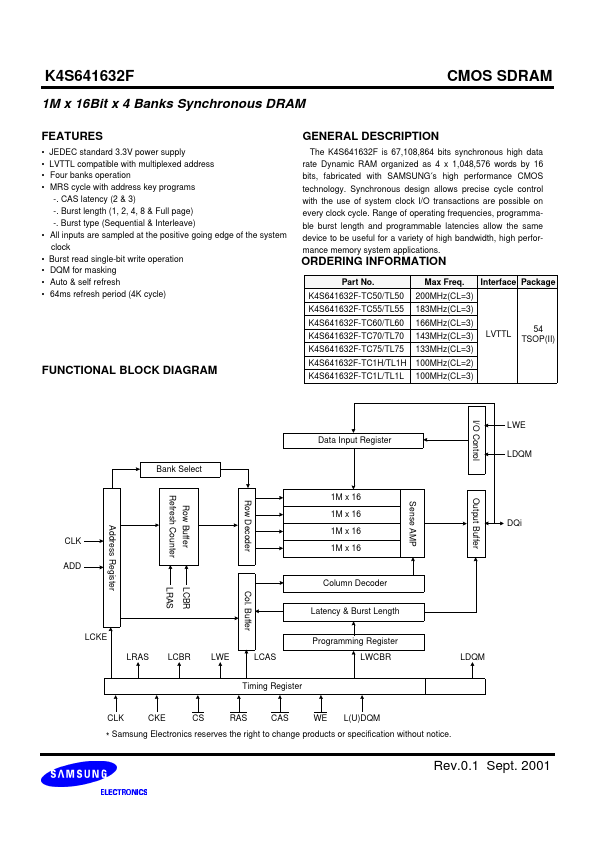

1M x 16Bit x 4 Banks...