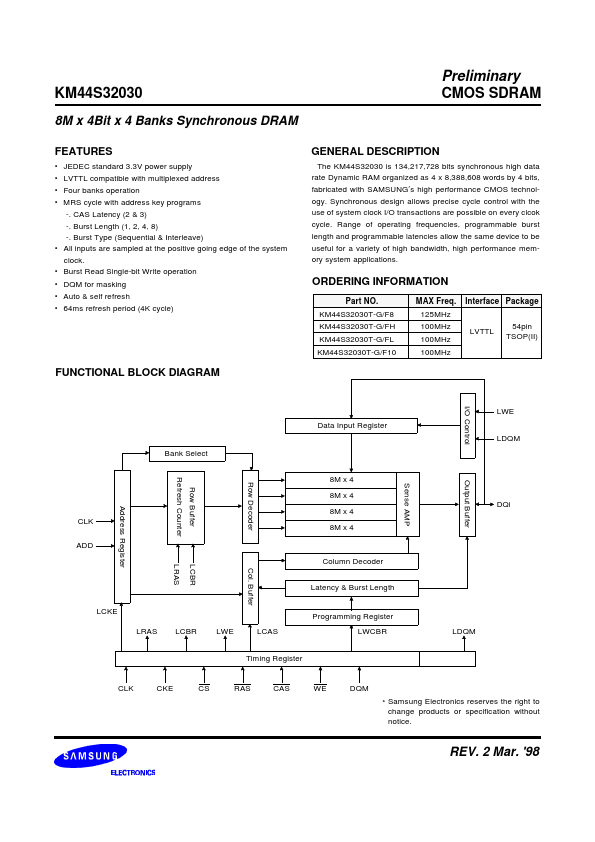

KM44S32030 Key Features

- JEDEC standard 3.3V power supply

- LVTTL patible with multiplexed address

- Four banks operation

- MRS cycle with address key programs -. CAS Latency (2 & 3) -. Burst Length (1, 2, 4, 8) -. Burst Type (Sequential & Inte

- All inputs are sampled at the positive going edge of the system clock

- Burst Read Single-bit Write operation

- DQM for masking

- Auto & self refresh

- 64ms refresh period (4K cycle)