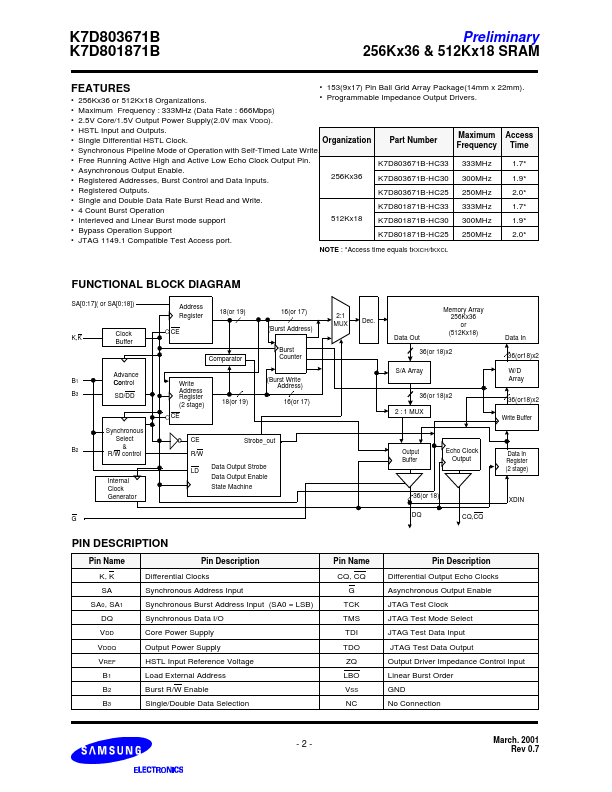

K7D803671B Key Features

- 256Kx36 or 512Kx18 Organizations

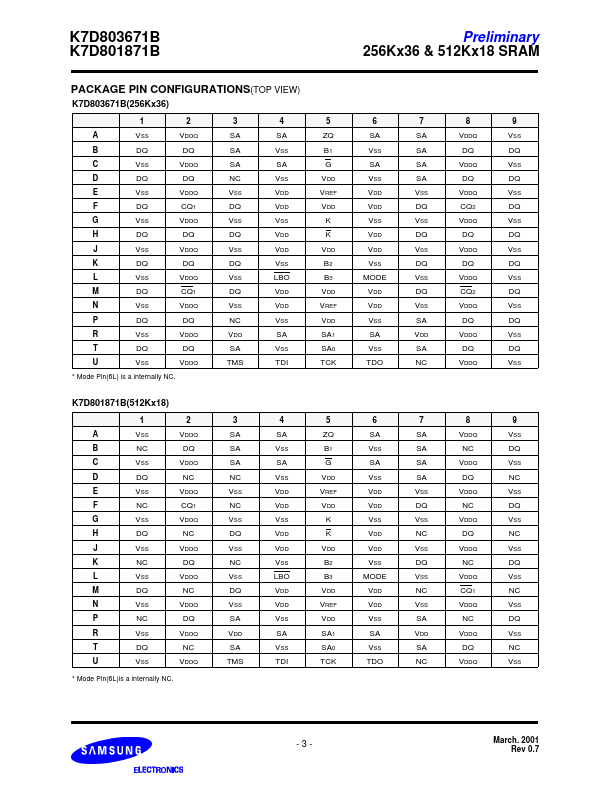

- 153(9x17) Pin Ball Grid Array Package(14mm x 22mm)

- Programmable Impedance Output Drivers

- Maximum Frequency : 333MHz (Data Rate : 666Mbps)

- 2.5V Core/1.5V Output Power Supply(2.0V max VDDQ)

- HSTL Input and Outputs

- Single Differential HSTL Clock

- Synchronous Pipeline Mode of Operation with Self-Timed Late Write

- Free Running Active High and Active Low Echo Clock Output Pin

- Asynchronous Output Enable