LC89052T

LC89052T is Digital Audio Interface Receiver manufactured by SANYO.

.. Ordering number : ENN7457

CMOS LSI

Digital Audio Interface Receiver

1. Overview

The LC89052T is an audio LSI that demodulates according to the data format for the data transferred between digital audio devices via the IEC 60958/61937 and EIAJ CP-1201. It supports sampling frequencies of up to 192k Hz and output data lengths up to 28 bits. Despite it is pact and made in a low cost, the LC89052T includes a built-in oscillator and serial data input circuits and allows the system microcontroller to read the sub-code Q data and channel status. It supports low-power modes that allow low-voltage operation. It also supports a lower power mode, which is suitable for application that requires long battery life, such as cell phones, PDAs, and portable audio devices.

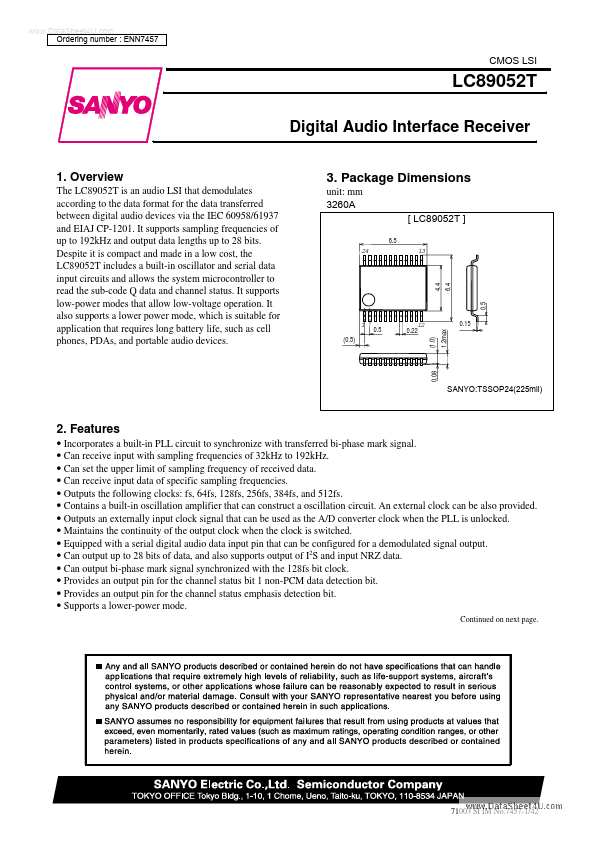

3. Package Dimensions unit: mm 3260A [ LC89052T ]

6.5 24 13

4.4 6.4

1 (0.5)

(1.0)

2. Features

- Incorporates a built-in PLL circuit to synchronize with transferred bi-phase mark signal.

- Can receive input with sampling frequencies of 32k Hz to 192k Hz.

- Can set the upper limit of sampling frequency of received data.

- Can receive input data of specific sampling frequencies.

- Outputs the following clocks: fs, 64fs, 128fs, 256fs, 384fs, and 512fs.

- Contains a built-in oscillation amplifier that can construct a oscillation circuit. An external clock can be also provided.

- Outputs an externally input clock signal that can be used as the A/D converter clock when the PLL is unlocked.

- Maintains the continuity of the output clock when the clock is switched.

- Equipped with a serial digital audio data input pin that can be configured for a demodulated signal output.

- Can output up to 28 bits of data, and also supports output of I2S and input NRZ data.

- Can output bi-phase mark signal synchronized with the 128fs bit clock.

- Provides an output pin for the channel status bit 1 non-PCM data detection bit.

- Provides an output pin for the channel status emphasis detection...