S93C66B

S93C66B is (S93Cx6B) CMOS SERIAL E2PROM manufactured by Seiko Instruments.

- Part of the S93C56B comparator family.

- Part of the S93C56B comparator family.

..

Rev. 3.1_01

CMOS SERIAL E2PROM

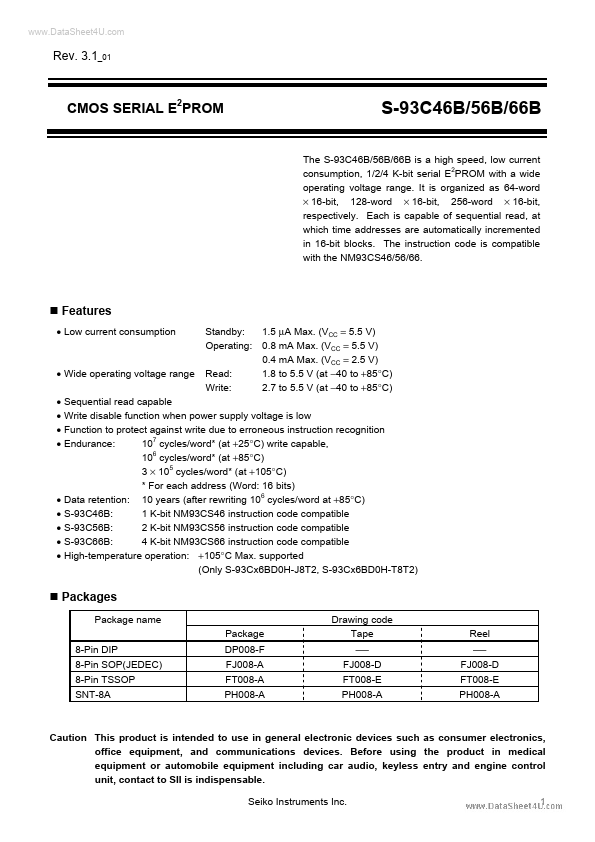

S-93C46B/56B/66B

The S-93C46B/56B/66B is a high speed, low current consumption, 1/2/4 K-bit serial E2PROM with a wide operating voltage range. It is organized as 64-word × 16-bit, 128-word × 16-bit, 256-word × 16-bit, respectively. Each is capable of sequential read, at which time addresses are automatically incremented in 16-bit blocks. The instruction code is patible with the NM93CS46/56/66.

- Features

- Low current consumption Standby: 1.5 µA Max. (VCC = 5.5 V) Operating: 0.8 mA Max. (VCC = 5.5 V) 0.4 mA Max. (VCC = 2.5 V) Read: 1.8 to 5.5 V (at

- 40 to +85°C) Write: 2.7 to 5.5 V (at

- 40 to +85°C)

- Wide operating voltage range

-...