LH521028A

Key Features

- Fast Access Times: 15/17/20/25/35 ns

- Wide Word (18-Bits) for: - Improved Performance - Reduced Component Count - Nine-bit Byte for Parity

- Transparent Address Latch

- Reduced Loading on Address Bus

- Low-Power Stand-by Mode when Deselected

- TTL Compatible I/O

- 5 V ± 10% Supply

- 2 V Data Retention

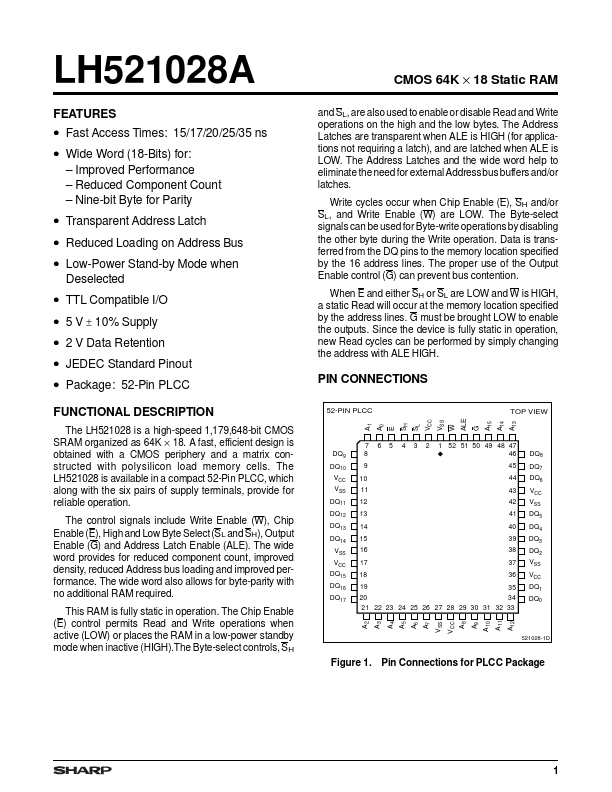

- JEDEC Standard Pinout

- Package: 52-Pin PLCC FUNCTIONAL DESCRIPTION The LH521028 is a high-speed 1,179,648-bit CMOS SRAM organized as 64K ×